基于 FPGA 的嵌入式系統設計為現代電子產品設計帶來了更大的靈活性,以 Altera 公司開發的 Nios II 軟核處理器為核心的SOPC(System on Programmable Chip)系統便是把嵌入式系統應用在 FPGA 上的典型例子。

關鍵字:

Nios SOPC 內核 開發板

0引言

I2C(Inter-Integrated Circuit)總線是一種由Phil-ips公司開發的兩線式串行總線,用于連接微控制器及其外圍設備。由于I2C總線僅用兩根信號線,并支持多主控工作方式,所以I2C總線在電子產品設備中應用非常普遍。文獻[1]使用NiosⅡ的PIO接口模擬I2C時序完成對接口芯片的讀寫,而目前基于NiosⅡ的IP核越發豐富。基于此,本文使用免費的IP核--I2C-Master Core,實現了對I2C接口芯片的讀寫操作,擴充了一種新的設計方法。本文首先介紹了I2C總

關鍵字:

Nios I2C 總線接口 C語言

本文針對特定的用戶環境,提出采用Altera的SOPC(片上可編程系統)解決方案,利用NiosⅡ軟核處理器和FPGA(現場可編程門陣列)配置靈活、IP資源豐富、硬件設計和軟件編程方便的特點,通過擴展IDE(集成開發環境)接口,以硬盤作為存儲媒介,實現多路VOD系統的設計方案。該系統體積小、成本相對低廉,體現了嵌入式電子產品的優勢。與傳統的VOD系統相比,使用范圍更具針對性,裝配更靈活,升級擴展更方便,具有很廣闊的前景。

關鍵字:

視頻 點播系統 嵌入式 軟核 Nios 基于

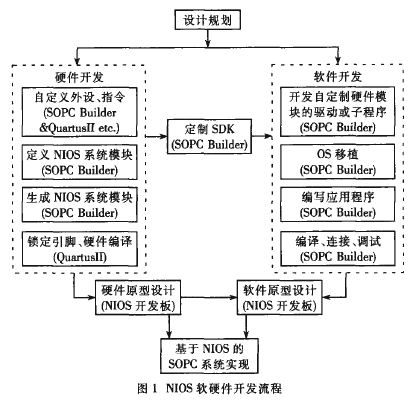

摘要:本文以硬盤錄像機的設計為例, 介紹了NIOS 嵌入式軟核的工作流程、開發步驟和使用方法。

關鍵詞: NIOS ;嵌入式處理器;硬盤錄像

隨著現場可編程邏輯陣列( FPGA) 技術的日益成熟,基于片上的可編程( SOPC)的嵌入式處理器受到越來越多的關注。特別是Altera公司推出的NIOS嵌入式處理器軟核, 通過軟件編程的方法可靈活地實現嵌入式處理器的功能, 并且針對FPGA進行性能優化, 可以大大提高系統性能。此外,NIOS還具有片上調試功能,因此便于系統的設計和調試.本文以硬盤錄

關鍵字:

NIOS 嵌入式處理器 硬盤錄像

嵌入式系統一般由嵌入式微處理器、外圍硬件設備、嵌入式操作系統以及用戶應用程序四部分組成,其發展主要體現在芯片技術的進步上,以及在芯片技術限制下的算法與軟件的進步上。

隨著芯片制造技術的發展,嵌入式系統的結構也隨之發生了重大變革,從基于微處理器的嵌入式系統到基于微控制器的嵌入式系統,繼而將可編程邏輯pld(programmable logic device)技術引入到嵌入式系統設計中,進而又發展到soc(system on chip),最終將pld與嵌入式處理器結合而成為sopc(system o

關鍵字:

嵌入式系統 單片機 微處理器 nios μClinux 操作系統

Altera公司宣布開始提供新的Cyclone® III版Nios® II嵌入式評估套件。Nios II評估套件是功能豐富的低成本平臺,為嵌入式設計人員提供快捷簡單的實踐方式來評估Nios II處理器、SOPC Builder系統設計軟件及其定制應用軟件。

在獨特的樹脂玻璃箱中,Nios II 評估套件含有一塊Cyclone III入門電路板和觸摸屏LCD,通過屏幕觸摸,支持開發人員啟動網絡和音頻圖像處理等實例應用軟件。對于剛開始FPGA處理器設計的軟件開發人員,它還是理想的開發

關鍵字:

嵌入式系統 單片機 Altera Cyclone Nios II 開發工具

摘要:首先分析研究nios ii軟核處理器系統的啟動過程,然后在多處理器系統中設計一nios ii 的啟動方案,此方案通過外部cpu控制nios ii處理器系統的啟動。

關鍵詞:nios ii;系統啟動;多處理器系統;sopc

引言

nios ii 處理器是altera公司設計的一款基于fpga的32位risc嵌入式軟核處理器,具有32位指令集、數據通路及地址空間,是其可編程系統芯片(sopc)的核心。nios ii系統采用altera公司設計的一套avalon總線交換結構,aval

關鍵字:

嵌入式系統 單片機 nios ii 系統啟動 多處理器系統 sopc

液晶顯示器按其功能可分為筆段式和點矩陣式液晶顯示器,后者又可以分為字符點陣式和圖形點陣式液晶顯示器。圖形點陣式液晶顯示器不僅可顯示數字、字符等內容,還能顯示漢字和任意圖形。但此類液晶顯示屏屬于非一般模式類設備,在Nios II中不能直接開發使用。

對于一個全新的外部設備,Nios II有更好的解決方案快速的掌握它的控制方法。按照設備的電器要求,使用Nios II的已有的基本控制設備(例如通用輸入輸出端口PIO)掌握新設備的控制特性與方法。當充分理解新設備的特性后就可以按照Nios II的硬件抽象

關鍵字:

嵌入式系統 單片機 Nios II 液晶顯示器 MCU和嵌入式微處理器

Altera和Synopsys宣布,Altera流行的Nios II處理器內核可通過DesignWare Star IP包提供許可給客戶使用。這一新品擴展了Altera現有的FPGA和HardCopy®結構化ASIC產品供給,幫助Nios II用戶將設計移植到標準單元ASIC。Nios II處理器內核是應用最廣泛的FPGA處理器,其客戶群有5,000多家電子設備生產商,包括世界上排名靠前的OEM。

通過DesignWare Star IP包,設計人員可以使用一流Star IP供應商開發的

關鍵字:

嵌入式系統 單片機 Altera Synopsys Nios II MCU和嵌入式微處理器

1 引言

作為地面數字電視的組網方式之一,單頻網(SingleFrequendy Network,SFN)具有節省頻率資源和能實現大范圍無線覆蓋的特點,在世界各地得到廣泛應用。組建單頻網要解決的一個難題是發射機的同步問題,為此單頻網引入了GPS接收機和單頻網適配器來實現全網的同步。

2006年8月具有自主知識產權的DTMB標準正式確定為中國地面數字廣播傳輸標準,該標準中,系統的信號幀與絕對時間同步,與DVB-T等標準相比,實現單頻網更具優勢。

2 單頻網適配器總體實現方案

單頻網主要有中心發射站

關鍵字:

嵌入式系統 單片機 Nios II DTMB 網適配器 通信基礎

在FPGA系統中,實現對外部A/D數據采集電路的控制接口邏輯,由于其邏輯功能不是很復雜,因此可采用自定義的方式。采用這種方法進行設計有兩種途徑。①從軟件上去實現。這種方案將NIOS處理器作為一個主控制器,通過編寫程序來控制數據轉換電路。由于NIOS處理器的工作頻率相對于外部設備來說要高出許多,故此種方法會造成CPU資源極大的浪費;②用FPGA 的邏輯資源來實現A/D采集電路的控制邏輯。FPGA有著豐富的邏輯資源和接口資源,在其中實現并行的數據采集很少會受到硬件資源的限制,在功能上,設計的接口控制邏輯相當于

關鍵字:

模擬技術 電源技術 0708_A 雜志_高校園地 NIOS-II 數據采集 模擬IC 電源

摘 要:本設計應用Altera 公司的Cyclone II系列的FPGA(現場可編程門陣列)實現了對步進電機正弦波可變細分控制,并在FPGA中進行了具體驗證和實現。該方案綜合運用了電流跟蹤型SPWM技術、PI調節、片上可編程系統SOPC技術、EDA技術等。步進電機控制系統用FPGA實現了Nios II軟核處理器與硬件邏輯電路集于一體,發揮了處理器的靈活性和數字邏輯電路高速性,有效地解決了步距角的高細分問題,細分數最高達4096,而且細分數可自動調節。實驗

關鍵字:

嵌入式系統 單片機 步進電機驅動器 Nios II 嵌入式

摘 要:針對傳統Otsu局部遞歸分割方法很難實時實現的局限性,提出了一種適合現場可編程門陣列(FPGA)中Nios II軟核處理器實現的快速Otsu局部遞歸分割算法,該算法的思路是把一次Otsu分割得到的目標區域作為新的圖像再進行一次Otsu分割,得到的結果作為最終分割閾值.利用并行Nios II和VHDL實現的硬件加速邏輯協同設計保證算法的實時實現。實驗結果表明,在不同的背景下,利用本文設計能夠實時穩定地對目標分割提取,具有較好的魯棒性。 關鍵字:FPGA&nb

關鍵字:

嵌入式系統 單片機 FPGA Nios II 0tsu分割 局部遞歸 嵌入式

引 言

循環碼是最重要的一類線性分組糾錯碼,而BCH碼又是目前發現的性能很好且應用廣泛的循環碼,它具有嚴格的代數理論,對它的理論研究也非常透徹。BCH碼的實現途徑有軟件和硬件兩種。軟件實現方法靈活性強且較易實現,但硬件實現方法的工作速度快,在高數據速率和長幀應用場合時具有優勢。FPGA(現場可編程門陣列)為DSP算法的硬件實現提供了很好的平臺,但如果單獨使用一片FPGA實現BCH編解碼,對成本、功耗和交互速度都不利。最新的SoC(片上系統)設計方法可以很好地解決這個問題。

關鍵字:

嵌入式系統 單片機 Nios SoC BCH編解碼 IP核

nios介紹

Nios II

前不久,Altera 正式推出了Nios II系列32位RSIC嵌入式處理器。Nios II系列軟核處理器是Altera的第二代FPGA嵌入式處理器,其性能超過200DMIPS,在Altera FPGA中實現僅需35美分。Altera的Stratix 、Stratix GX、 Stratix II和 Cyclone系列FPGA全面支持Nios II處理器,以后推出 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473