基于Nios II的I2C總線接口的實現

0引言

本文引用地址:http://www.j9360.com/article/82352.htmI2C(Inter-Integrated Circuit)總線是一種由Phil-ips公司開發的兩線式串行總線,用于連接微控制器及其外圍設備。由于I2C總線僅用兩根信號線,并支持多主控工作方式,所以I2C總線在電子產品設備中應用非常普遍。文獻[1]使用NiosⅡ的PIO接口模擬I2C時序完成對接口芯片的讀寫,而目前基于NiosⅡ的IP核越發豐富。基于此,本文使用免費的IP核--I2C-Master Core,實現了對I2C接口芯片的讀寫操作,擴充了一種新的設計方法。本文首先介紹了I2C總線結構和工作原理,然后詳細說明了基于NiosⅡ的I2C-Master Core的使用方法,最后給出了C語言的編程代碼。

1 I2C總線基本原理

I2C總線是由數據線SDA和時鐘SCL構成的串行總線,可發送和接收數據。在CPU與被控IC之間、進行雙向傳送,最高傳送速度100 kbit/s。

I2C總線在傳送數據的過程中共有4種基本類型信號,分別是:開始信號、數據傳輸信號、應答信號和結束信號。

a)開始信號:SCL為高電平時,SDA由高電平向低電平跳變,開始傳送數據。所有的命令都必須在開始條件以后進行。

b)結束信號:SCL為低電平時,SDA由低電平向高電平跳變,結束傳送數據。所有的操作都必須在停止條件以前結束。總線開始和停止數據傳送的時序如圖1所示。

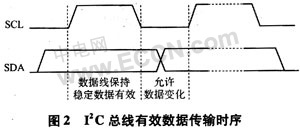

c)數據傳輸信號:在開始條件以后,時鐘信號SCL的高電平周期期問,當數據線穩定時,數據線SDA的狀態表示數據有效,即數據可以被讀走,開始進行讀操作。在時鐘信號SCL的低電平周期期間,數據線上數據才允許改變。每位數據需要一個時鐘脈沖。I2C總線的數據位傳送時序如圖2所示。

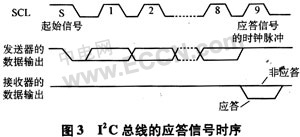

d)應答信號:接收數據的從器件收到8 bit數據后,向發送數據的主控器件發出特定的低電平脈沖,表示已收到數據。這要求主器件必須產生一個與確認位相應的額外時鐘脈沖(第9個脈沖)。若主控器件確認失敗,主控器件必須發送一個數據結束信號給從器件。這時從器件必須使SDA線保持高電平,使主控器件能產生停止條件。總線的應答信號時序見圖3。

2 I2C接口芯片AT24C01/02工作原理

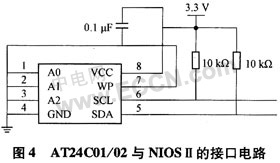

AT24CXX系列芯片是采用I2C總線標準的常用的串行EEROM芯片。本文以AT24C02為例介紹。AT24C02具有256×8(2 k)bit的存儲容量,即總共32頁,每頁有8字節的容量。每次寫入數據是從主器件發送來的片內選擇地址開始寫人,如果寫到頁末尾,主器件還在繼續發送的話,不會自動轉到下一頁,而是從該頁的頭地址開始繼續寫入,覆蓋該頁的原有數據,而造成數據丟失。AT24C02工作于從器件方式,它的地址由外圍的3個引腳A2、A1、A0決定,如圖4所示。在I2C總線上總共可以連接8個AT24C02接口芯片,每個器件硬件地址與控制寄存器的地址內容保持一致,就能夠自由地與主控器件進行數據傳輸。

1)器件字節寫操作

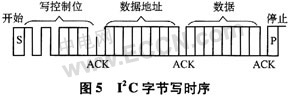

在字節寫模式下,發送器件寫控制字,控制字包括4位固定器件碼,3位片選碼,以及一位低電平的寫控制位。主器件在收到從器件產生應答信號后,主器件發送一個8位字節地址寫入AT24C02。主器件在收到從器件的另一個應答信號后,再發送數據到被尋址的存儲單元。AT24C02再次應答,并在主器件產生停止信號后開始內部數據的擦寫,在內部擦寫過程中,AT24C02不再應答主器件的任何請求。時序見圖5。

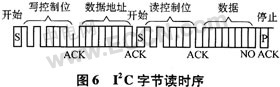

2)器件隨機地址讀操作

對AT24C02讀操作的初始化方式和寫操作時一樣,僅把R/W位置為1。圖6所示為AT24C02隨機地址讀時序圖。隨機讀操作允許主器件對寄存器的任意字節進行讀操作,主器件首先通過發送起始信號、從器件地址和它想讀取的字節數據的地址執行一個偽寫操作。在AT24C02應答之后,主器件重新發送起始信號和從器件地址,此時R/W位置1,AT24C02響應并發送應答信號,然后輸出所要求的一個8位字節數據,主器件不發送應答信號但產生一個停止信號。

3 I2C-Master Core工作原理

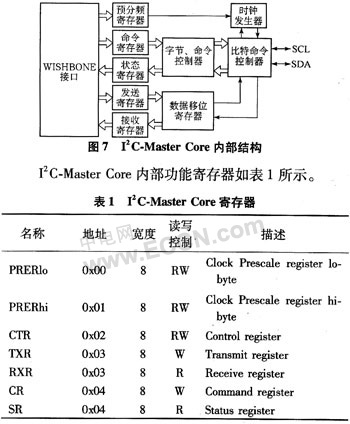

基于NiosⅡ的IP核應用非常簡便,因此越發受到青睞。Altera公司已經提供了一些通用的IP核可供使用,但沒有提供I2C核。文獻[3]提供了免費的I2C-Master Core,經筆者的應用與長時間測試,證明該Mas-ter Core使用方便可靠,工作穩定。該Master Core的內部結構如圖7所示,主要由時鐘發生器、字節命令控制器、比特命令發生器和數據移位寄存器4個模塊組成。其他模塊是一些相關接口和臨時數據存儲器。

時鐘發生器主要是產生SCL信號,該時鐘的頻率可由預分頻寄存器設置,控制子計算公式如下:

![]()

例如:SCL頻率為100kHz,NiosⅡ工作頻率為50 MHz,則預分頻=99,PRERlo=99,PRERhi=0。

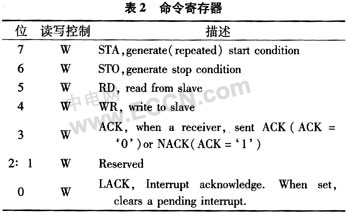

字節命令控制器在字節級連接命令寄存器、狀態寄存器和比特命令控制器。通過將表2所示命令寄存器相應的比特位置1,可以產生I2C接口的開始、結束、確認等信號,以及讀寫控制。這些有效控制通過字節命令控制器轉送到比特命令控制器,使其發生作用,在信號產生后,這些比特位自動清0。

NiosⅡ向發送寄存器寫數據實現數據輸出,讀接收寄存器獲取從器件輸出的數據。數據的讀寫是否完成可通過中斷或查詢方式得知。如采用中斷方式,狀態寄存器中的IF狀態位置1;如采用查詢方式,數據處理過程中,狀態位TIP置1,處理完畢后置1。

4應用實例

筆者在NiosⅡIDE7.1環境下編寫了使用該Mas-ter Core的C語言代碼,現把部分主程序代碼列出。

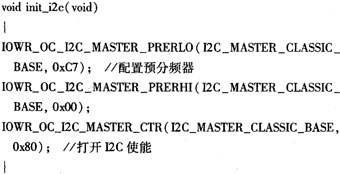

1)IP-Master Core初始化

完成對預分頻器的設置,確定SCL時鐘頻率;控制寄存器中I2C-Master Core使能位置1,使其工作。

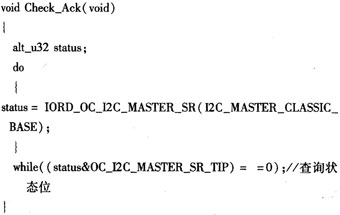

2)查詢確認信號

數據收發是否完成,通過查詢TIP狀態位來確定。

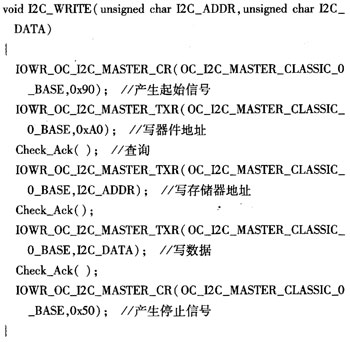

3)寫字節操作

單字節寫入按圖5操作流程:

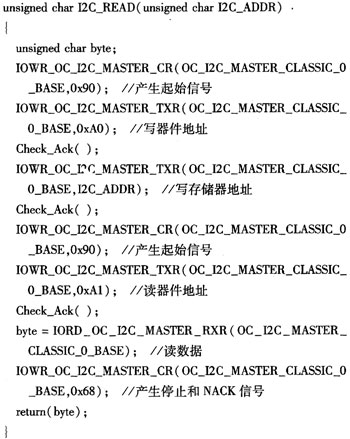

4)隨即地址讀操作

隨即地址讀字節按圖6流程操作:

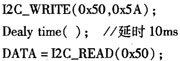

以上是使用I2C-Master Core的關鍵代碼,若向地址0xS0寫入0x5A,再將其讀出,可按下面寫法:

若操作正確,DATA的值應該位為0x5A。

5結束語

本文探討了使用免費I2C-Master Core的方法,方便地實現了基于Nios Ⅱ的I2C接口芯片的開發,為I2C的電子工程設計使用提供了一種簡單快捷的方法。

分頻器相關文章:分頻器原理

評論