- 《Cortex-M3可編程片上系統原理及應用》系統化、模塊化地介紹了Cypress公司的PSoC5內所集成的ARMCortex-M3CPU硬核處理器結構及指令集、PSoC5內各個功能單元的結構以及基于PSoCCreator2.0軟件的片上系統的設計流程。

- 關鍵字:

Cortex-M3 可編程片上系統 PSoC5 PSoCCreator

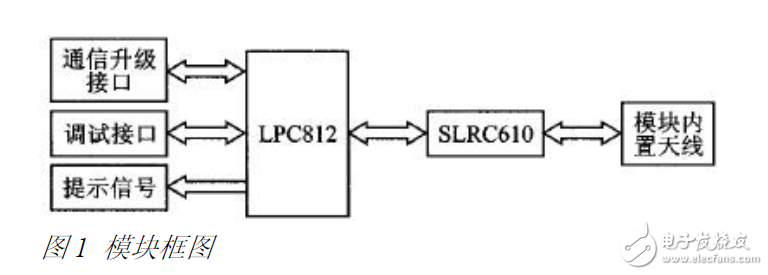

- 近年來,隨著我國電網改造工作及智能電網建設的持續推進,推廣智能電表已成為其中的重要內容,也是緩解電力供需矛盾、節能降耗、提高社會效益和經濟效益的有效手段,電網智能化催熱智能電表的大力發展。

- 關鍵字:

智能電表 PLC ZigBee Cortex-M0 方案

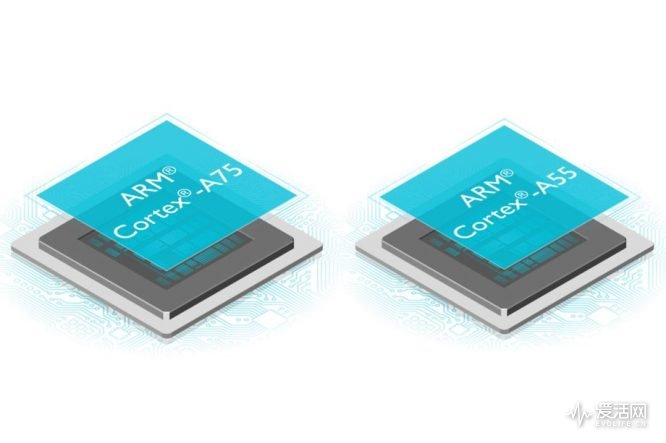

- Computex是一場PC業界的盛會,行業大佬匯聚一堂,x86平臺在這場展會中唱主角,各種筆記本臺式機爭相斗艷,卻不料ARM偏偏選擇在這個節骨眼上公布Cortex-A75/A55架構,而且盡其所能地把AI、機器學習、AR/VR等流行關鍵詞拼命往自己身上拉,似乎是要把人們的關注從以PC為主的計算領域吸引到移動計算上來。

ARM在新一代的移動計算核心里所采用的架構依舊是那套大小核做法——big.LITTLE,不過這一次它們換了個叫法:Dynamiq

- 關鍵字:

ARM Cortex-A75

- 2017年3月21日,ARM在北京召開新聞發布會,正式宣布推出全新的DynamlQ技術。該項技術作為未來ARM Cortex-A系列處理器的基礎,代表了多核處理設計行業的轉折點,其靈活多樣性將重新定義更多類別設備的多核體驗,覆蓋從端到云的安全、通用平臺。DynamlQ技術將被廣泛應用于汽車、家庭以及數不勝數的各種互聯設備,以實現更先進的人工智能。

- 關鍵字:

ARM Cortex-A

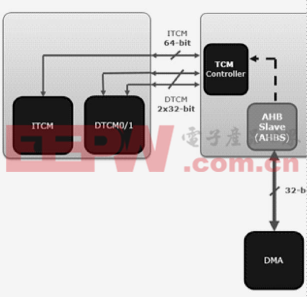

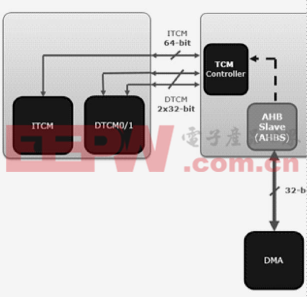

- 對于那些需要低功耗、成本效益和中等性能的嵌入式系統而言,ARM Cortex M系列無疑是首選的處理器系列。 Cortex M系列中最早得到應用的是其光譜中的小部分產品: Cortex M0用于實現最低的成本,Cortex M0+用于實現最高 的能效,Cortex M3用于實現功耗與性能之間的最佳平衡, Cortex M4用于實現那些需要數字信號處理(DSP)功能的應 用。 該系列中最高性能的Cortex M7的首批應用現已開

- 關鍵字:

Cortex M7 內存

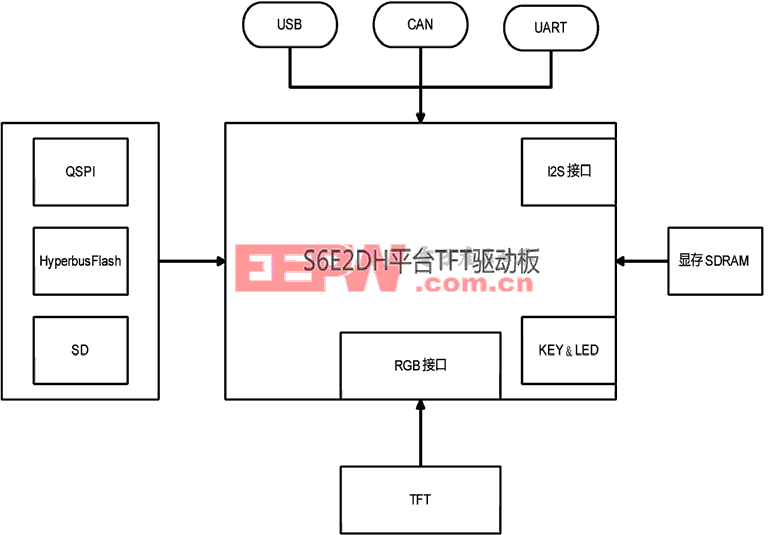

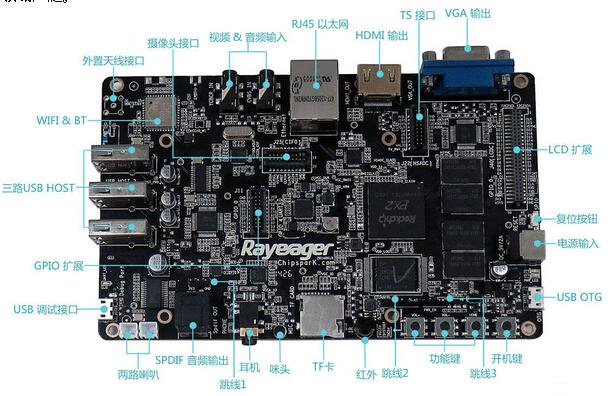

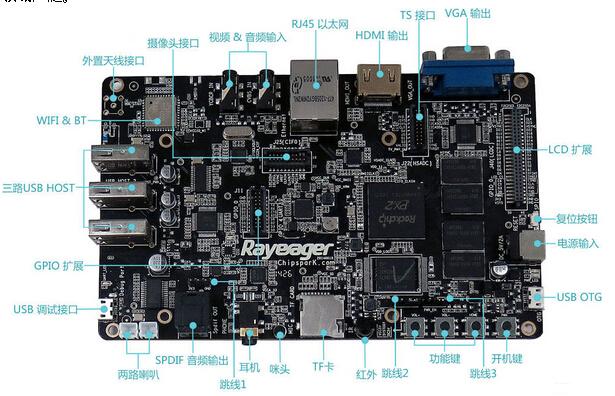

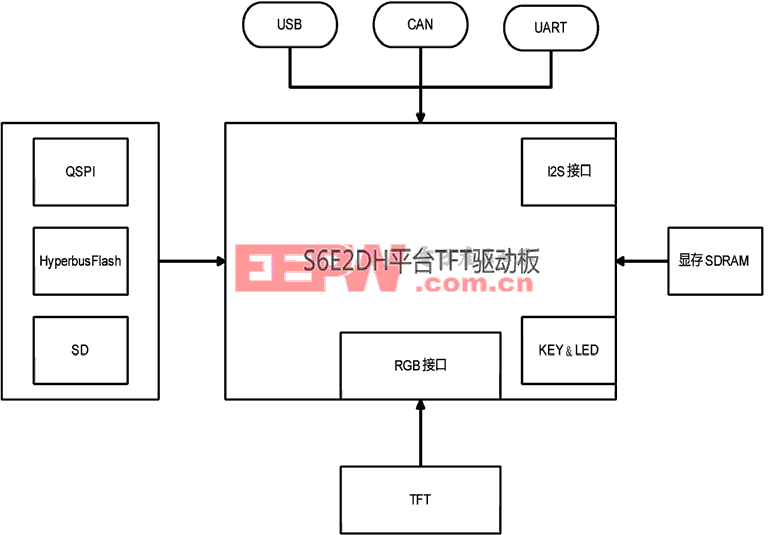

- 引言 ? ? ?目前在物聯網相關應用中,包括使能家具顯示面板、 工控顯示面板、手持設備、人臉識別等領域都在逐步由傳統 的黑白點陣LCD或者段式LCD顯示向彩色TFT屏顯示發展, 主要是因為彩色TFT屏幕顯示內容豐富而且價格也越來越便 宜,但是基于彩色TFT的顯示面板大都顯示內容復 雜,效果多,素材占用資源大,這就對微處理器的 處理能力提出了更高的要求,現在大多數的方案都 是基于ARM9、A8或者更高端的處理器去實現相關 功能,這些方案實現起來開發復雜,開發周期長, BOM成本

- 關鍵字:

Cypress Cortex-M4 顯示

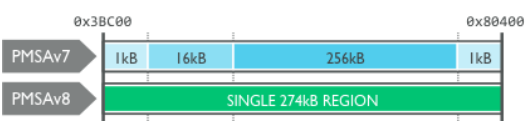

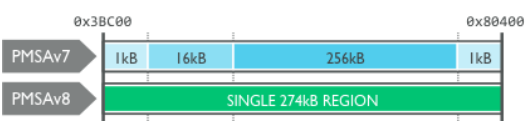

- ARM? Cortex?-M23采用TrustZone?技術,是尺寸最小、能效最高的處理器。小型嵌入式應用對芯片的安全性能有嚴格要求,基于ARMv8-M基線架構的Cortex-M23處理器則是最佳解決方案。 本文中,我將帶各位領略全新Cortex-M23處理器的強大特色: Cortex-M23最重要的特色是加入了TrustZone安全基礎技術 極緊湊的架構與布線 強化的調試糾錯和追溯能力(對開發商的生產力提高至關重要) 存儲保護單元獲得改善(該單元定義軟件組件的訪問許可,全新設計提

- 關鍵字:

ARM Cortex-M23

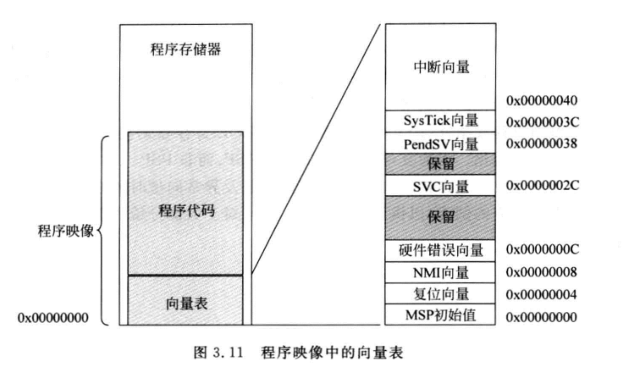

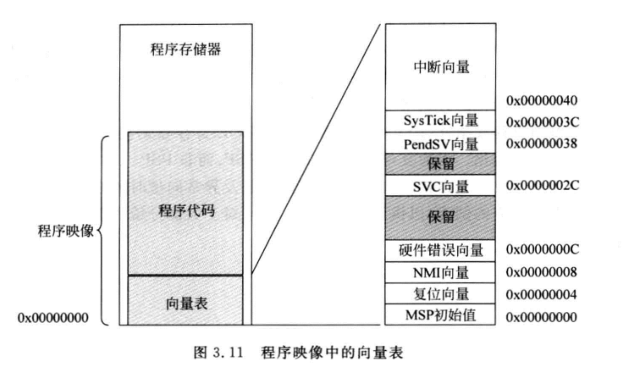

- 我們先來看看程序映像。

通常,Cortex-M0處理器的程序映像時從地址0x00000000處開始的。 程序映像開始處時向量表,其中包含了異常的其實地址(向量),每個中斷向量的地址都等于“異常號*4”,比如,外部IRQ0的異常類型為16,因此其向量地址為16*4=0x40。這些向量的最低位都被置為1,以表示使用thumb指令。向量表的大小由實際使用的中斷個數決定。 向量表中包含了MSP的初始值,它存儲在向量表的頭四個字節。 復位時,處理器首先讀取向量

- 關鍵字:

Cortex-M0 處理器

- 基于ARM Cortex處理器的片上系統(SoC)解決方案適用于多種嵌入式設計細分市場,如物聯網、電機控制、醫療、汽車、家電自動化等。我們的處理器品種豐富且基于同一個標準架構,針對不同的產品市場提供廣泛而豐富的性能與成本組合。

Cortex系列處理器主要基于3大產品類型量身開發,A系列:運行復雜系統的精細高端應用;R系列:高性能硬實時系統;M系列:低功耗、確定性、成本敏感的微控制器,專門優化以滿足其需求。

最先采用ARMv8-M架構的2款處理器為Cortex-M23和Cortex-M33。

- 關鍵字:

ARM Cortex-M33

- 為了管理中斷請求的優先級并處理其他異常,Cortex-M0處理器內置了嵌套中斷控制器(NVIC)。NVIC的一些可編程控制器控制著中斷管理功能,這些寄存器被映射到系統地址空間里,它們所處的區域被稱為系統控制空間(SCS)。

NVIC有以下特性: 靈活的中斷管理; 支持嵌套中斷; 向量化的異常入口 中斷屏蔽 靈活的中斷管理 Cortex-M0處理器中,每一個外部中斷都可以被使能或者禁止,并且可以被設置為掛起狀態或者清除狀態。處理器的中斷可以是信號

- 關鍵字:

Cortex-M0 中斷

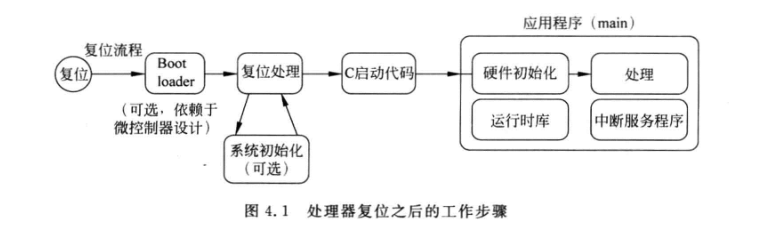

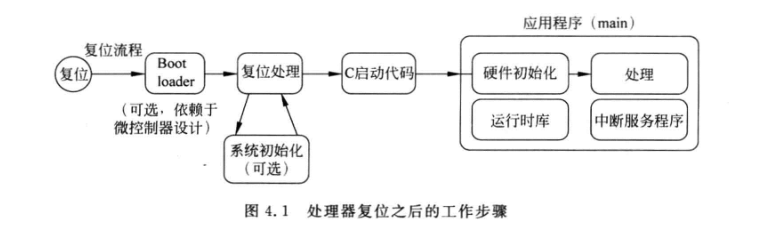

- 嵌入式系統編程入門 微控制器是如何啟動的 為了保存編譯號的二進制程序代碼,大多數的現代微控制器都會包含片上flash存儲器。有些微控制器還可能有一個獨立的啟動ROM,里面裝有Bootloader程序。微控制器啟動后,再執行flash的用戶程序前,Bootloader會首先運行。 在復位流程中,處理器會取出MSP的初始化值和復位向量,然后開始執行復位處理,這些信息都放在一個叫做啟動代碼的程序文件中。啟動代碼中的復位處理可能還會旅行初始化的職責,比如時鐘控制電路和鎖相環PLL的初始化。有些情況下,系

- 關鍵字:

Cortex-M0

- 異常會引起程序控制的變化。在異常發生時,處理器停止當前的任務,轉而執行異常處理程序,異常處理完成后,會繼續執行剛才的任務。異常分為很多種,中斷是其中之一。Cortex-M0處理器最多支持32個外部中斷(IRQ)和一個不可屏蔽中斷(NMI),中斷事件的處理叫做中斷服務程序(ISR),中斷一般由片上的IO口的外部輸入產生(邊沿觸發和電平觸發)。 Cortex-M0處理器上可用的中斷數量不確定,由廠商決定,最多32個外部中斷。如果系統的外設很多,由于中斷數目有限,多個中斷源可能使用同一個中斷連接。 除了

- 關鍵字:

Cortex-M0 中斷

- 為了管理中斷請求的優先級并處理其他異常,Cortex-M0處理器內置了嵌套中斷控制器(NVIC)。NVIC的一些可編程控制器控制著中斷管理功能,這些寄存器被映射到系統地址空間里,它們所處的區域被稱為系統控制空間(SCS)。 NVIC有以下特性: 靈活的中斷管理; 支持嵌套中斷; 向量化的異常入口 中斷屏蔽 靈活的中斷管理 Cortex-M0處理器中,每一個外部中斷都可以被使能或者禁止,并且可以被設置為掛起狀態或者清除狀態。處理器的中斷可以是信號級的(在中斷服務程序清除中斷請求以前,外設的

- 關鍵字:

Cortex-M0 NVIC

- 歲末年終,一波波購物海潮澎湃來襲,圣誕季與新年季也正式拉開了帷幕。給晚輩,給愛人,給孩子的過節禮品你都預備好了嗎?這一次,讓ARM來為你推薦幾款新鮮新穎的小玩藝兒吧,相信一定會陪同你珍愛的人渡過異乎尋常的假期。 【Hush智能耳塞:睡得平穩,起得準時】 歇息和節日老是一對形影不離的好朋友,繁忙了一年,總算可以趁著節日的空檔好好補個覺。快來嘗嘗Hush吧!它可是號稱“世界上第一款智能耳塞”呢。Hush拙劣地將熱遲鈍回憶泡沫耳塞和播放舒緩音效的耳機相結合,無效地將樂音和攪擾阻隔在好夢外。固然,用戶也不

- 關鍵字:

ARM Cortex-M4

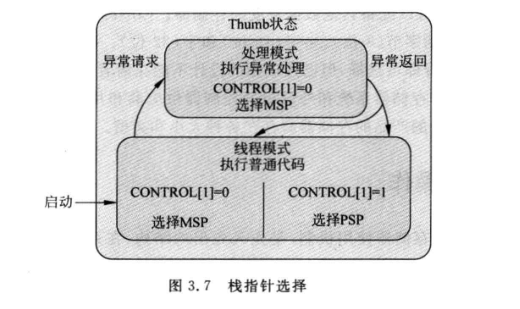

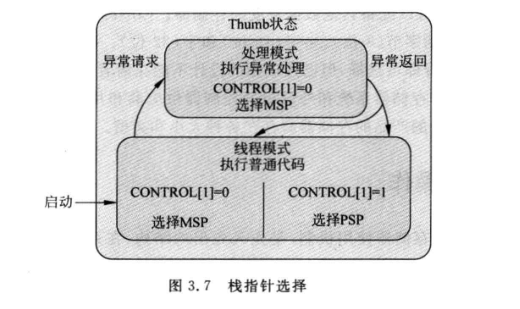

- 棧空間作為一種存儲器使用機制,是“先入先出”的結構,在系統空間中用作臨時數據的存儲。棧空間操作的關鍵之一為棧指針寄存器,每次執行棧操作時,棧指針的內容會自動移動。在M0處理器中,棧指針為R13(SP),而且物理上存在兩個棧指針,MSP,PSP,但每次只會使用一個,由CONTROL寄存器以及處理器的運行狀態決定。 向棧中存入數據叫“壓棧”(使用PUSH指令),回復數據叫“出棧”(使用POP指令)。根據架構不同,有些處理器壓棧后地址增加,有些地址減小。Cortex-M0操作基于“滿遞減”的棧模型,意味著

- 關鍵字:

Cortex-M0 寄存器

cortex-m3介紹

您好,目前還沒有人創建詞條cortex-m3!

歡迎您創建該詞條,闡述對cortex-m3的理解,并與今后在此搜索cortex-m3的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473