Cortex-M3可編程片上系統原理及應用

《Cortex-M3可編程片上系統原理及應用》系統化、模塊化地介紹了Cypress公司的PSoC5內所集成的ARMCortex-M3CPU硬核處理器結構及指令集、PSoC5內各個功能單元的結構以及基于PSoCCreator2.0軟件的片上系統的設計流程。主要內容包括:PSoC設計導論,PSoC5 CPU及存儲子系統,PSoC5CPU指令系統,PSoC5公共資源,PSoC編程和調試接口功能,基于PSoCCreator的程序設計,定時器、計數器和PWM模塊,LCD顯示驅動模塊,FC總線模塊,USB總線模塊,通用數字塊UDB,模擬前端模塊,ADC和DAC模塊,電容感應模塊,數字濾波器模塊和uC-OS/Ⅲ操作系統。本書可作為從事Cypress可編程片上系統設計的設計人員的參考用書,也可作為大學本科生和研究生教材,同時也可作為Cypress公司相關內容的培訓教材。

本文引用地址:http://www.j9360.com/article/201706/348140.htm

第1章 PSoC設計導論 1

1.1 微控制器基礎 1

1.1.1 微控制器的涵義 1

1.1.2 微控制器編程語言 2

1.2 可編程片上系統PSoC概述 3

1.2.1 PSoC發展概述 3

1.2.2 PSoC設計方法 5

1.3 PSoC5設計流程 7

1.3.1 硬件設計流程 8

1.3.2 軟件設計流程 9

1.4 PSoC5的結構及功能 10

1.4.1 PSoC5系統結構概述 10

1.4.2 數字子系統結構及功能 10

1.4.3 模擬子系統結構及功能 13

1.4.4 輸入/輸出引腳功能 14

1.5 PSoC5器件概述 15

1.5.1 PSoC5引腳分布 15

1.5.2 PSoC5器件分類和資源 16

第2章 PSoC5 CPU及存儲子系統 19

2.1 Cortex-M3內核結構概述 19

2.1.1 Cortex-M3內核結構特性 19

2.1.2 流水線結構 20

2.1.3 寄存器 20

2.1.4 操作模式 23

2.1.5 SysTick定時器 23

2.1.6 存儲器空間映射 23

2.1.7 異常及處理 26

2.2 嵌套向量中斷控制器 26

2.2.1 中斷控制器的特性 26

2.2.2 中斷使能 28

2.2.3 中斷優先級 29

2.2.4 電平/脈沖中斷 30

2.2.5 中斷的執行 30

2.2.6 PSoC5中斷特性 31

2.2.7 中斷控制器和功耗模式 34

2.3 高速緩存控制器 35

2.4 PHUB和DMA控制器 36

2.4.1 PHUB 36

2.4.2 DMA控制器 38

2.4.3 訪問DMAC 44

2.4.4 DMAC傳輸模式 45

2.4.5 PHUB和DMAC寄存器列表 46

2.5 PSoC5存儲器系統 47

2.5.1 SRAM存儲器結構及功能 47

2.5.2 非易失性鎖存器結構及功能 48

2.5.3 Flash程序存儲器結構及功能 49

2.5.4 EEPROM存儲器結構及功能 50

第3章 PSoC5 CPU指令系統 51

3.1 Cortex-M3指令尋址模式 51

3.2 Cortex-M3 CPU指令集 53

3.2.1 Cortex-M3指令集概述 53

3.2.2 CMSIS函數 54

3.2.3 存儲器訪問指令 54

3.2.4 通用數據處理指令 61

3.2.5 乘法和除法指令 69

3.2.6 飽和指令 71

3.2.7 比特位操作指令 72

3.2.8 分支和控制指令 74

3.2.9 雜項操作指令 77

3.3 Cortex-M3 匯編語言編程模型 80

第4章 PSoC5公共資源 82

4.1 時鐘管理 82

4.1.1 內部振蕩器 83

4.1.2 外部振蕩器 84

4.1.3 DSI時鐘 86

4.1.4 相位鎖相環 86

4.1.5 USB時鐘 86

4.2 電源管理 87

4.2.1 電源模式 87

4.2.2 電源監控 89

4.3 看門狗定時器 89

4.4 復位 90

4.4.1 復位模塊功能介紹 90

4.4.2 復位源 91

4.5 I/O系統和布線資源 92

4.5.1 I/O系統特性 92

4.5.2 I/O驅動模式 94

4.5.3 DSI控制數字I/O 97

4.5.4 模擬I/O引腳 99

4.5.5 LCD驅動引腳 100

4.5.6 電容感應觸摸引腳 100

4.5.7 SIO功能和特性 100

4.5.8 上電時I/O配置 101

4.5.9 過電壓容限 101

4.5.10 端口中斷控制器單元 102

第5章 PSoC編程和調試接口功能 104

5.1 測試控制器 104

5.1.1 測試控制器結構 104

5.1.2 SWD接口規范 104

5.1.3 PSoC5 SWD的特性 106

5.2 Cortex-M3調試和跟蹤 107

5.2.1 內核調試 108

5.2.2 系統調試 109

5.3 非易失性存儲器編程 110

第6章 基于PSoC Creator的程序設計 112

6.1 PSoC Creator軟件功能 112

6.2 匯編語言GPIO控制程序的設計 113

6.2.1 創建和配置工程 113

6.2.2 查看和設置公共資源 114

6.2.3 編寫GPIO匯編語言控制程序 115

6.3 C語言GPIO控制程序的設計 119

6.3.1 使用C語言指針對GPIO端口控制 120

6.3.2 調用API函數對GPIO端口控制 120

6.3.3 PSoC5的SRAM內函數定位 126

6.4 中斷服務程序的設計 128

6.4.1 創建和配置工程 128

6.4.2 添加IP核資源到設計 128

6.4.3 IP核參數配置和連接 129

6.4.4 中斷服務程序的設計 131

6.4.5 下載并調試工程 133

第7章 定時器、計數器和PWM模塊 134

7.1 定時器模塊特性 134

7.2 定時器模塊結構 134

7.2.1 時鐘選擇 135

7.2.2 使能/禁止模塊 136

7.2.3 輸入信號特性 136

7.2.4 操作模式 137

7.2.5 中斷使能 141

7.2.6 寄存器列表 141

7.3 PWM控制LED顯示的實現 142

7.3.1 創建和配置工程 142

7.3.2 編寫軟件程序 146

7.3.3 編程及調試 147

第8章 LCD顯示驅動模塊 148

8.1 LCD的工作原理 148

8.1.1 LCD物理結構 148

8.1.2 LCD液晶分類 149

8.2 LCD驅動特性 154

8.3 LCD驅動系統 154

8.4 LCD功能描述 155

8.4.1 LCD DAC 155

8.4.2 LCD配置選項 156

8.4.3 LCD驅動模塊 156

8.4.4 UDB 159

8.4.5 DMA 159

8.5 段式LCD顯示的實現 160

8.5.1 段式LCD的功能 160

8.5.2 段式LCD的參數配置 162

8.5.3 編寫軟件程序 167

8.5.4 編程及調試 169

第9章 I2C總線模塊 170

9.1 I2C總線模塊概述 170

9.2 I2C總線實現原理 171

9.2.1 I2C總線模塊結構 171

9.2.2 典型的I2C數據傳輸 171

9.2.3 I2C總線寄存器及操作 172

9.3 I2C總線操作模式 173

9.3.1 從模式 173

9.3.2 主模式 174

9.3.3 多主模式 175

9.4 I2C模塊通信的實現 176

9.4.1 系統實現原理 176

9.4.2 創建和配置工程 177

9.4.3 編寫軟件程序 181

9.4.4 編程及調試 183

第10章 USB總線模塊 184

10.1 USB總線模塊概述 184

10.2 USB模塊結構 184

10.2.1 串行接口引擎SIE 185

10.2.2 仲裁器 186

10.3 USB模塊工作條件 187

10.3.1 工作頻率 187

10.3.2 工作電壓 188

10.3.3 收發器 188

10.3.4 端點 188

10.3.5 傳輸類型 188

10.3.6 中斷 189

10.4 邏輯傳輸模式 189

10.4.1 非DMA訪問 190

10.4.2 手工DMA訪問 190

10.4.3 控制端點的邏輯傳輸 193

10.5 PS/2和CMOS I/O模式 194

10.6 USB模塊寄存器列表 194

10.7 USB人體學輸入設備的實現 195

10.7.1 人體接口設備的原理 195

10.7.2 創建和配置工程 200

10.7.3 編寫軟件程序 204

10.7.4 編程及調試 205

第11章 通用數字塊UDB 207

11.1 通用數字塊概述 207

11.2 UDB模塊結構 208

11.2.1 PLD模塊結構及宏單元 208

11.2.2 數據通道模塊 209

11.2.3 狀態和控制模塊 212

11.3 交通燈控制電路的設計與實現 213

11.3.1 交通燈設計原理 213

11.3.2 交通燈控制電路的設計 213

11.3.3 引腳分配 218

11.3.4 設計下載與測試 218

11.4 靜態時序分析 218

第12章 模擬前端模塊 220

12.1 模擬比較器 220

12.1.1 輸入和輸出接口 220

12.1.2 LUT 220

12.2 運算放大器模塊 221

12.3 可編程SC/CT模塊 223

12.3.1 單純的放大器 224

12.3.2 單位增益 225

12.3.3 可編程增益放大器 225

12.3.4 互阻放大器 227

12.3.5 連續時間混頻器 228

12.3.6 采樣混頻器 228

12.3.7 Δ-Σ調制器 230

12.3.8 跟蹤和保持放大器 231

12.4 精密參考源 231

12.5 基于混頻器的精確整流實現 233

12.5.1 整流器設計原理 233

12.5.2 創建和配置工程 233

12.5.3 編寫軟件程序 237

12.5.4 編程及調試 237

第13章 ADC和DAC模塊 238

13.1 Δ-ΣADC模塊 238

13.1.1 Δ-ΣADC模塊概述 238

13.1.2 Δ-ΣADC結構 239

13.1.3 Δ-Σ ADC操作模式 241

13.2 SAR ADC模塊 242

13.2.1 SAR ADC模塊概述 242

13.2.2 SAR ADC模塊的工作原理 242

13.3 DAC模塊 243

13.4 基于SAR ADC的數字電壓表實現 246

13.4.1 創建和配置工程 246

13.4.2 編寫軟件程序 249

13.4.3 編程及調試 250

13.5 基于Δ-Σ ADC的數字電壓表實現 251

13.5.1 創建和配置工程 251

13.5.2 編寫軟件程序 253

13.5.3 編程及調試 254

13.6 IDAC值顯示的實現 254

13.6.1 創建和配置工程 255

13.6.2 編寫軟件程序 258

13.6.3 編程及調試 258

第14章 電容感應模塊 259

14.1 電容感應模塊的結構 259

14.2 電容感應Δ-Σ算法 262

14.3 電容感應觸摸的實現 263

14.3.1 創建和配置工程 263

14.3.2 編寫軟件程序 266

14.3.3 編程及調試 267

第15章 數字濾波器模塊 268

15.1 數字濾波器模塊概述 268

15.2 數字濾波器模塊結構 269

15.2.1 控制器 269

15.2.2 FSM RAM 270

15.2.3 數據通道 272

15.2.4 地址計算單元 273

15.2.5 總線接口和寄存器描述 274

15.3 基于DFB的數字濾波器實現 276

15.3.1 系統結構概述 276

15.3.2 元件參數配置 276

15.3.3 DMA配置向導 280

15.3.4 編寫軟件程序 282

15.3.5 編程及調試 283

第16章 μC-OS/III操作系統 284

16.1 μC-OS/III操作系統概述 284

16.1.1 操作系統的作用 284

16.1.2 μC-OS/III操作系統內核特征 285

16.1.3 μC/OS-III操作系統文件的結構 288

16.1.4 μC/OS-III操作系統應用程序結構分析 289

16.2 μC-OS/III操作系統內核及功能 296

16.2.1 單任務和多任務處理 296

16.2.2 臨界區 300

16.2.3 任務管理 300

16.2.4 準備列表 301

16.2.5 調度 301

16.2.6 上下文切換 302

16.2.7 中斷管理 302

16.2.8 等待列表 303

16.2.9 時間管理 303

16.2.10 定時器管理 303

16.2.11 資源管理 304

16.2.12 消息傳遞 305

16.2.13 多個對象等待處理 307

16.2.14 存儲器管理 308

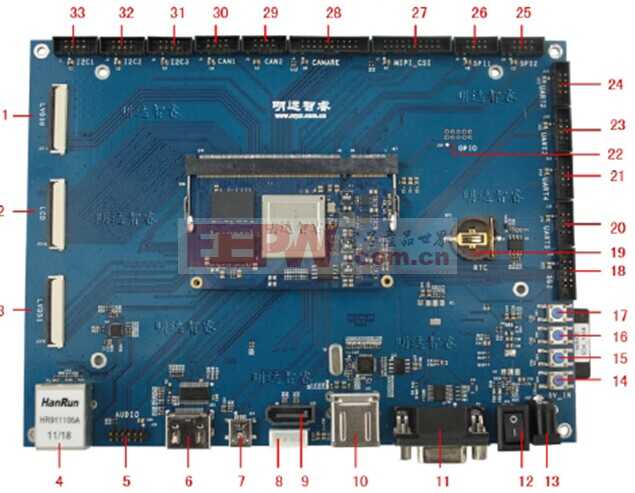

16.3 PSoC5硬件系統的構建 309

16.4 添加中斷代碼到ISR中 310

16.4.1 添加中斷代碼到ProbeUART_TxISR.c中 310

16.4.2 添加中斷代碼到ProbeUART_RxISR.c中 311

16.5 配置引腳 311

16.6 運行設計 312

16.7 啟動μC/Probe工具 313

參考文獻 316

評論