asic-to-fpga 文章 進入asic-to-fpga技術社區(qū)

利用APTIX MP3C和Spartan-IIE FPGA實現(xiàn)數(shù)據(jù)系統(tǒng)的

- 隨著數(shù)字電路設計的規(guī)模及復雜程度的提高,對其進行測試試驗證所花費的時間和費用也隨之提高,所以減少測試驗證成本是當前數(shù)字電路設計的關鍵。

- 關鍵字: Spartan-IIE APTIX MP3C FPGA

基于FPGA的高級數(shù)據(jù)加密AES中的字節(jié)替換設計

- 介紹AES中的字節(jié)替換算法原理并闡述基于FPGA的設計和實現(xiàn)。為了提高系統(tǒng)工作速度,在設計中應用了流水線技術。

- 關鍵字: FPGA AES 數(shù)據(jù)加密 字節(jié)

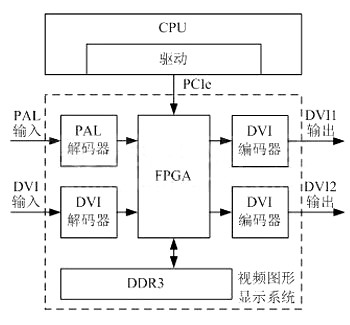

用FPGA控制CLC5958型A/D轉(zhuǎn)換器實現(xiàn)的高速PCI數(shù)據(jù)采集卡

- 詳細介紹CLC5958的內(nèi)部結構和基本用法,提出一種基于FPGA和PCI總線的高速數(shù)據(jù)采集卡設計方案,并通過仿真驗證了該方案的可行性。

- 關鍵字: 高速 PCI 數(shù)據(jù)采集 實現(xiàn) 轉(zhuǎn)換器 控制 CLC5958 A/D FPGA

多處理器系統(tǒng)芯片設計:IP重用和嵌入式SOC開發(fā)的邏輯方法

- Tensilica公司總裁兼CEO Chris Rowen博士 硅芯片技術的飛速發(fā)展給SOC設計帶來新的危機。為了保持產(chǎn)品的競爭力,新的通信產(chǎn)品、消費產(chǎn)品和計算機產(chǎn)品設計必須在功能、可靠性和帶寬方面有顯著增長,而在成本和功耗方面有顯著的下降。 與此同時,芯片設計人員面臨的壓力是在日益減少的時間內(nèi)設計開發(fā)更多的復雜硬件系統(tǒng)。除非業(yè)界在SOC設計方面采取一種更加有效和更加靈活的方法,否則投資回報障礙對許多產(chǎn)品來說就簡直太高了。半導體設計和電子產(chǎn)品發(fā)明的全球性步伐將會放緩。 SOC設計團隊會面臨一系列嚴峻

- 關鍵字: Tensilica SoC ASIC

聯(lián)華選擇Agilent 93000 SOC測試儀

- --全球領先的半導體專工廠采用93000進行高速數(shù)字信號和混合信號測試-- 安捷倫科技日前宣布,聯(lián)華電子已經(jīng)購買一部Agilent 93000 SOC系列測試儀,進行基于結構的高速數(shù)字信號和混合信號測試。聯(lián)華電子將使用93000測試計算設備、PC和游戲控制臺使用的大容量復雜SOC。93000系列能夠擴容及測試廣泛的一系列應用,幫助聯(lián)華電子降低測試成本,加快其客戶的產(chǎn)品開發(fā)周期。 “Agilent 93000提供了混合信號結構測試解決方案,并兼容廣大客戶的高端模塊核心。聯(lián)華電子

- 關鍵字: 聯(lián)華 SoC ASIC

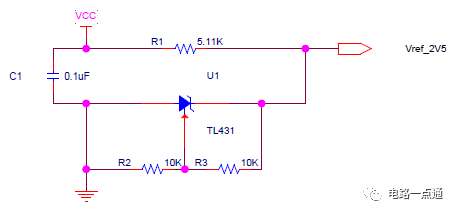

高性能ASIC和微處理器供電電源

- 今天的高性能ASIC和微處理器芯片消耗的功率可超過150瓦。對于1 V~1.5 V的供電電壓,這些器件所需要的電流可輕易超過100 A。通過采用多相直流/直流轉(zhuǎn)換器,為此類器件供電的任務可變得更容易處理。 目前,可擴展控制器允許設計人員為特定的直流/直流轉(zhuǎn)換器選擇所需要的相數(shù)。可擴展性還允許幾個控制器同步并聯(lián)使用。電路板上基于PLL 技術的時鐘發(fā)生器為控制器同步提供了支持。 表1 根據(jù)設計所使用的相數(shù),比較同步降壓調(diào)節(jié)器設計的關鍵參數(shù)。圖中的例子為12V~1.2V 100A降壓調(diào)節(jié)器 圖1

- 關鍵字: 供電電源 ASIC 微處理 模擬IC 電源

asic-to-fpga介紹

您好,目前還沒有人創(chuàng)建詞條asic-to-fpga!

歡迎您創(chuàng)建該詞條,闡述對asic-to-fpga的理解,并與今后在此搜索asic-to-fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對asic-to-fpga的理解,并與今后在此搜索asic-to-fpga的朋友們分享。 創(chuàng)建詞條

熱門主題

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司