導讀:在音箱中,有一個很不起眼的部件,說它不起眼,是因為在音箱的表面上根本找不到它,一般除了想深入了解音箱的人外,也幾乎沒有人關注它的存在。而音箱離了它,又根本無法工作,它就是分頻器。下面就隨小編一起了解一下分頻器的作用吧!

1. 分頻器的作用—簡介

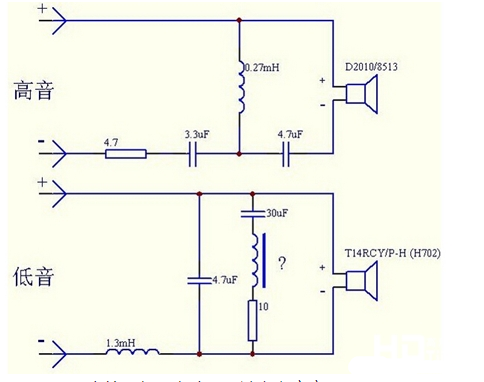

分頻器是指將不同頻段的聲音信號區分開來,分別給于放大,然后送到相應頻段的揚聲器中再進行重放,在高質量聲音重放時,需要進行電子分頻處理。它可以把輸入信號的頻率作出處理,使得輸出信號的頻率滿足相關關系的電路。分頻器主要分為模擬分頻器和數字

關鍵字:

分頻器 分頻器的作用

1、前言

分頻器是FPGA設計中使用頻率非常高的基本單元之一。盡管目前在大部分設計中還廣泛使用集成鎖相環(如Altera的PLL,Xilinx的DLL)來進行時鐘的分頻、倍頻以及相移設計,但是,對于時鐘要求不太嚴格的設計,通過自主設計進行時鐘分頻的實現方法仍然非常流行。首先這種方法可以節省鎖相環資源,再者這種方式只消耗不多的邏輯單元就可以達到對時鐘的操作目的。

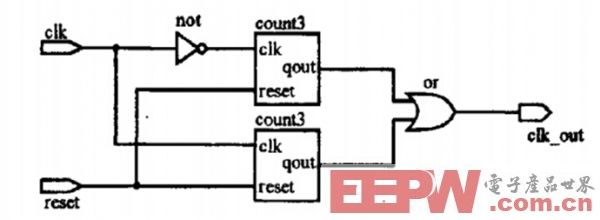

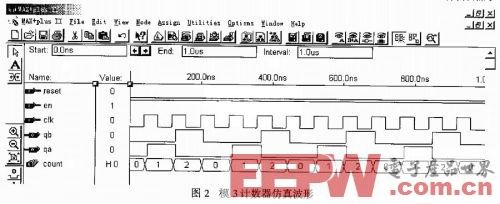

2、整數倍分頻器的設計

2.1 偶數倍分頻

偶數倍分頻器的實現非常簡單,只需要一個計數器進行計數就能實現。如需要N分頻

關鍵字:

FPGA 分頻器 PLL

1引言

CPLD(ComplexprogrammableLogicDevice,復雜可編程邏輯器件)和FPGA(FieldprogrammableGatesArray,現場可編程門陣列)都是可編程邏輯器件,它們是在PAL、GAL等邏輯器件基礎上發展起來的。同以往的PAL、GAL相比,FPGA/CPLD的規模比較大,適合于時序、組合等邏輯電路的應用。它可以替代幾十甚至上百塊通用IC芯片。這種芯片具有可編程和實現方案容易改動等特點。由于芯片內部硬件連接關系的描述可以存放在磁盤、ROM、PROM、或E

關鍵字:

FPGA CPLD 分頻器

1.引言

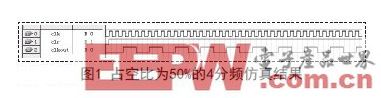

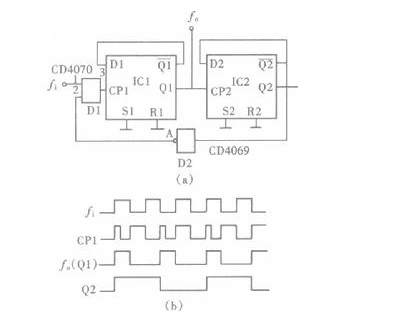

分頻器是數字系統中非常重要的模塊之一,被廣泛應用于各種控制電路中。在實際中,設計人員往往需要將一個標準的頻率源通過分頻技術以滿足不同的需求。常見的分頻形式主要有:偶數分頻、奇數分頻、半整數分頻、小數分頻、分數分頻。在某些嚴格的情況下,還有占空比的要求。其中非等占空比的偶數分頻器和奇數分頻器其實現比較容易,但對于半整數分頻器和占空比為50%的奇數分頻器實現比較困難。

本文首先介紹了各種分頻器的實現原理,并結合VHDL硬件描述語言對其進行了仿真,最后提出一個可控的通用分頻器的設計方法,該方法可實

關鍵字:

FPGA 分頻器

Analog Devices, Inc. (NASDAQ:ADI),全球領先的高性能信號處理解決方案供應商,最近發布了一款時鐘緩沖器和分頻器 ...

關鍵字:

時鐘緩沖器 分頻器 IC AD9508

Analog Devices, Inc. (NASDAQ:ADI),全球領先的高性能信號處理解決方案供應商,最近發布了一款時鐘緩沖器和分頻器IC(集成電路)AD9508,該電路結合了高速、極低抖動(12 kHz至20 MHz頻段為41 fs)及可選分頻功能。該1.65 GHz 時鐘緩沖器設計用于要求具有最佳SNR(信噪比)性能的超高速數據轉換的通信、儀器儀表、防務和航空航天設備。

關鍵字:

ADI 緩沖器 分頻器

摘要:首先分析了應用于倍頻電路的預置可逆分頻器的工作原理,推導了觸發器的驅動函數。并建立了基于simulink 和FPGA 的分頻器模型,實驗結果表明分頻器可以實現預置模和可逆分頻功能,滿足倍頻電路需要。1. 前言鎖相

關鍵字:

倍頻電路 預置 分頻器

摘要:首先分析了應用于倍頻電路的預置可逆分頻器的工作原理,推導了觸發器的驅動函數。并建立了基于simulink 和FPGA 的分頻器模型,實驗結果表明分頻器可以實現預置模和可逆分頻功能,滿足倍頻電路需要。1. 前言鎖相

關鍵字:

FPGA 應用于 倍頻電路 分頻器

本文采用動態TSPC結構,利用TSMC 90nm 1P9M 1.2VCMOS工藝,設計了一個適用于WLAN IEEE802.11a標準的雙模前置分 ...

關鍵字:

WLAN IEEE80211a 雙模 分頻器

調音臺教程之分頻器、揚聲器和音箱 一、 分頻與分頻器 分頻是指將音頻信號分成高頻段、中頻段和低頻段。 ...

關鍵字:

教程 分頻器 揚聲器 音箱

摘要:首先分析了應用于倍頻電路的預置可逆分頻器的工作原理,推導了觸發器的驅動函數。并建立了基于simulink 和FPGA 的分頻器模型,實驗結果表明分頻器可以實現預置模和可逆分頻功能,滿足倍頻電路需要。 1. 前言

關鍵字:

應用于 倍頻電路 分頻器 預置

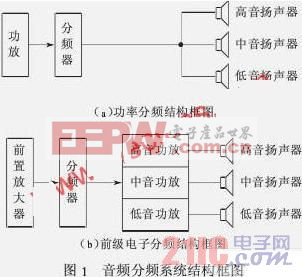

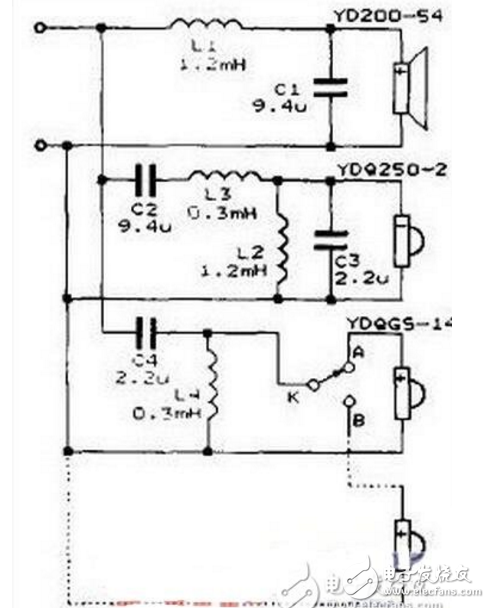

1 引言 揚聲器系統的分頻器分為前級分頻和功率分頻2類。前級分頻是前級電

關鍵字:

分頻器

電路設計、噪聲分析及仿真

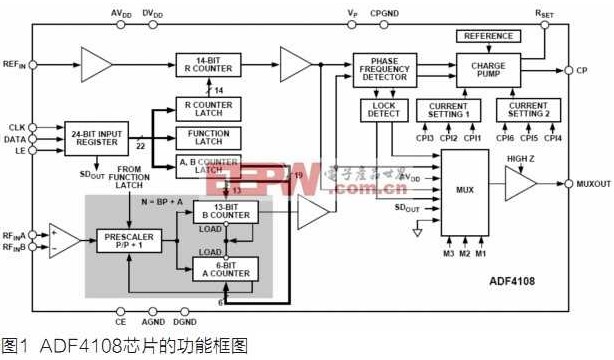

ADF4108主要由一個低噪聲數字鑒相器(PDF)、一個精密電荷泵、一個可編程參考分頻器、可編程A(6bit)及B(13bit)分頻計數器和一個雙模分頻器(P/P+1)構成。在這里,隨模式控制高、低電平的不同,雙模分頻器采用兩個不同的分頻模數P+1和P。雙模分頻器的輸出同時驅動兩個可編程分頻器,他們分別預置在A和B(A<B),并進行減計數。在除A和除B分頻器未計數到零時,模式控制為高電平,雙模分頻器輸出頻率為f0/(p+1)。在輸入A(P+1)個周期之后,除A分頻

關鍵字:

分頻器 VCO ADF4108

近日,全球知名的射頻微波MMIC廠商HITTITE全新推出一款低噪聲可編程分頻器HMC794LP3E。該產品采用QFN SMT封裝,非常緊湊的封裝在一個3*3mm芯片中,這種設計使得該產品即使在功率敏感應用中仍有很好的相噪性能。

HMC794LP3E可處理0.2-2GHz的輸入信號,提供四種分頻(/1, /2, /3, /4)輸出。當輸入信號頻率是2GHz時,在100 kHz頻偏處的噪聲低于-160 dBc/Hz,在10MHz的殘余噪聲低于-166 dBc/Hz。SiGe BiCMOS 技術可以

關鍵字:

Hittite 分頻器 HMC794LP3E

分頻器介紹

分頻器定義

分頻器是音箱內的一種電路裝置,用以將輸入的音樂信號分離成高音、中音、低音等不同部分,然后分別送入相應的高、中、低音喇叭單元中重放。

分頻器是指將不同頻段的聲音信號區分開來,分別給于放大,然后送到相應頻段的揚聲器中再進行重放。在高質量聲音重放時,需要進行電子分頻處理。

分頻器作用

分頻器是音箱中的“大腦”,對音質的好壞至關重要。功放輸出的音樂訊號必須經過分頻器 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473