基于TMS320C6205的信號采集處理系統

0引言

本文引用地址:http://www.j9360.com/article/87219.htm典型的DSP(數字信號處理器)內部采用改進的哈佛結構和流水線技術,可以在單指令周期內完成乘加運算,具有較高的處理能力。一個典型的基于DSP的信號采集處理系統,通常由DSP、A/D轉換器、存儲器和相應的接口電路組成,大都做成PCI(外設部件互連)接口插卡形式和主控計算機一起工作。各種控制信息通過PCI發送給DSP,采集處理后的結果再通過PCI接口發送回主控計算機。PCI接口部分一般需要采用接口芯片來完成,這樣會顯著增加系統的設計調試難度,并使成本增加。而選用本身帶有PCI接口的DSP處理芯片就可以省去這一部分額外的電路,不但降低了開發難度,也降低了設備成本。TMS320C6205就是這樣一種帶有PCI接口的DSP芯片,本文重點討論基于這種芯片的信號采集處理系統的實現方法。

1 TMS320C6205芯片的技術特點

TMS320C6205是基于TMS320C6000平臺的高性能DSP,TMS320C6205源自TMS320C6201 B,一種有新的PCI接口且性能提高的DSP芯片。TMS320C6205工作在200 MHz時的最大處理能力達到了1 600 MIPS(百萬條指令每秒)。所有TMS320C6000系列DSP芯片在代碼上都有兼容性,TMS320C62x定點DSP都基于相同的CPU核心設計,通過指令的并行性獲得了較強的處理能力。該系列DSP芯片具有8個處理單元,包括2個乘法器和6個ALU(算術邏輯單元),所有的處理單元都可以并行工作,因此在每一個時鐘周期內最多可以同時執行8條指令。

TMS320C6205和TMS320C6201及TMS320C6201B具有高度的兼容性,這幾種DSP芯片在以下幾個方面完全相同:TMS320C6205的CPU與TMS320C6201B完全相同,因此為TMS320C6201所寫的代碼可以不加修改地在TMS320C6205上運行;多通道緩沖串口(McBSP)、時鐘、中斷選擇也完全相同;TMS320C6201與TMS320C6205的內部存儲空間也相同,都具有64kB的程序和數據存儲區。與TMS320C6201相比,TMS320C6205通過升級具有了更強的處理能力,升級后的TMS320C6205和TMS320C6201有以下不同:

a)EMIF(擴展存儲器接口總線)做了簡單修改,減少了芯片的引腳數。SDRAM(同步DRAM)和SB-SRAM(同步猝發SRAM)在EMIF上共用了相同的控制信號。這兩種信號是互斥的,因此在系統中只能在兩種類型的存儲器中任選一種。

b)為提高DMA(直接存儲器訪問)的數據吞吐量,4通道的DMA控制器為每一個通道都配備了專用的FIFO,這樣就無需對FIFO信號進行仲裁。

c)用PCI模塊代替了TMS320C6201B的HPI(主機接口),PCI模塊具有高性能的32 bit主/從PCI即插即用功能,支持33 MHz的桌上電腦PCI接口,與PCI本地總線規格2.2版兼容,該接口模塊可作為具有33 MHz、32 bit寬度地址數據的PCI主從對象使用,該模塊包含配置寄存器、校驗生成、校驗和系統錯誤檢測和報告(PERR#,SERR#)以及電源管理能力。

d)具備4線EEPROM串行接口,這樣,PCI的控制空間寄存器就可以從外部的串行EEPROM加載配置,PCI模塊無需DSP的干涉就可以實現自動初始化。

e)TMS320C6205的PLL有x1、x4、x6、x7、x8、x9、x10和x11等模式,這些模式可以通過CLKMODE0引腳和EMIF數據引腳的上推和下拉電阻來選擇。

f)TMS320C6205使用15C05(0.15μm)處理技術,通過電池處理技術提供更低的核電壓和功耗。

g)用上推和下拉電阻實現了自舉模式配置。

2 信號采集處理系統硬件設計

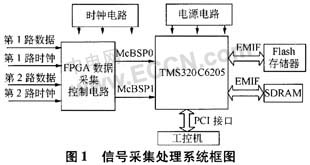

該系統硬件部分主要由DSP、FPGA(現場可編程門陣列)和存儲器構成,具體的硬件結構如圖1所示。

從圖中可以看出,信號采集處理系統的核心部分是TMS320C6205的DSP處理器,該DSP除了擔負信號處理任務外,還擔負著接收數據和輸出處理結果兩項任務。信號采集處理系統中的FPGA主要擔負數據采集和控制信號生成兩項任務。該系統的設計針對的是接收機解調后輸出的TCL電平的數字信號,因此數據采集部分比較簡單,就是將數據的時鐘作為觸發信號,根據觸發時刻的數據電平值來確定輸入數據是"0"還是"1",采集后的數據在FPGA內按照McBSP的數據規格成幀,然后通過McBSP寫入SDRAM中。該系統可以同時采集兩路數字信號,在采集電路與DSP之間通過DMA方式交換數據,由于DSP中有專門的DMA控制器,因此在數據交換時無需DSP干預,具有較高的處理效率。DSP所需的摔制信號也由FPGA產生,由于數據采集部分比較簡單,控制信號產生和數據采集可以共用同一片FPCA。DSP通過PC接口模塊與主機之間進行數據交換,由于PCI接口模塊具有完整的PCI接口功能,無需額外添加外部電路,因此接口部分的電路設計相對來說比較簡單。DSP與工控機進行數據交換時采用主從方式,DSP為主設備,工控機為從設備,兩者之間利用中斷響應進行數據通信,當DSP內部的輸出數據緩沖區被寫滿后,會發送一個中斷請求到主機的PCI總線上,PCI總線驅動程序響應該中斷并通過Windows的事件(Event)通知主機軟件讀出數據。為了擴充DSP的存儲空間,使DSP能滿足大速率信號的處理要求,信號采集處彈系統上集成了一片大容量存儲器,即SDRAM,具有較高的數據存取速度。信號采集處理系統上的Flash存儲器主要用來存儲DSP軟件,可通過PCI總線在主機端動態加載,這樣該信號采集處理系統就可根據不同的輸人數據進行不同處理,大大增加了系統使用時的靈活性。該系統還包括時鐘電路和電源電路,這些電路可以參照技術手冊的要求進行設計,電源電路可選用現成的電源模塊,這樣就可進一步降低電路設計難度。從總體上看,采用TMS320C6205構成的信號采集處理系統由于省去了額外的PCI接口電路,整個系統設計較簡潔,開發難度低,開發周期短,是一種較理想的硬件設計方法。

3基于DSP/BIOSⅡ的實時信號處理技術

信號采集處理系統中的DSP不但要實現高速信號處理,還需要處理數據的輸入輸出和中斷請求,這都要用到基本的任務調度和輸入輸出服務,DSP/BIOS實時基礎軟件提供了一個小的具有基小運行服務的固件核,開發者可以把這個核嵌入目標DSP中。DSP/BIOSⅡ是性能得到提升的第2代實時基礎軟件,利用該軟件可以縮短實時信號處理軟件的開發時間,并且可以顯著提高代碼的可重用性。

基于DSP/BIOSⅡ使信號處理技術實現起來比較簡單,整個配置過程都可以利用一個圖形化的界面來實現。首先,新建一個DSP/BIOS的配置文件,然后在"Syetem"文件夾下選擇"MEM",也就是存儲區管理模塊,在該模塊增加兩個新的MEM項,分別對應信號采集處理系統的SDRAM和Flash存儲器,設置好SDRAM和Flash存儲器的基地址和長度,至此片外存儲區的設置就全部完成了。由于DSP和數據采集部分通過McBSP交換數據,因此還需要對McBSP行設置。找到"CSL"也就是芯片支持庫文件夾,在McBSP選項下的McBSP配置管理(MsBSP ConfigurationManager)增加兩個新的McBSP的配置控制項,這兩個控制項分別對應McBSP0和McBSP1,然后設定這兩個配置項的參數,最關鍵的是接收模式和輸出模式的設置,接收和輸出均采用無壓擴的LSB方式,對于有壓擴的話音數據,可以根據需要選擇μ律或A律壓擴,這樣在數據讀寫的同時,利用DSP硬件也就完成了μ律或A律壓擴。McBSP可以實現數據的雙向傳輸,在本系統中只是從數據采集部分讀人數據,沒有用到其雙向數據傳輸功能。實際上,利用其雙向數據傳輸功能,結合μ律或A律可以很方便地實現話音的實時處理。所有配置都設置完后,將配置文件存盤加入當前工程,整個基于DSP/BIOS的配置便完成,在中斷響應函數配合下,就可實現整個實時處理軟件的開發。

實時處理軟件的數據流如圖2所示。從圖中可以看出,數據從McBSP通過DMA方式寫入SDRAM輸入緩沖區,整個輸入緩沖區劃分成若干片,數據處理部分按片進行處理,由于McBSP寫入的數據片與DSP處理的數據片不是同一個數據片,數據處理和數據寫入就可以同時進行,這是保證數據實時處理的一個關鍵。顯然,所分數據片數越多,可以有越長的處理時間,越適合進行一些復雜的算法,這樣要付出的代價就是輸出延時比較長,同時需要大的DSP片外存儲空間。數據處理后的結果存放在輸出緩沖區,輸出緩沖區的大小與輸入相同,當輸出緩沖區寫滿后,觸發PCI總線中斷處理函數,把處理后的結果通過PCI總線寫到主機緩沖區,主機程序從該緩沖區將數據讀出,存儲到計算機硬盤上的制定文件中。

顯然,該信號處理軟軟件中最關鍵的是McBSP的DMA中斷響應函數和PCI中斷響應函數,下面分別介紹這兩個函數。

DMA中斷響應函數的主要代碼如下:

從代碼中可以看出,DMA中斷響應函數最核心的部分是按照給定條件初始化DMA控制器,然后啟動DMA通道,開始接收數據。這里的給定條件主要是保證DMA的寫入地址符合要求,特別是在循環寫入的情況下不致發生地址沖突。DSP與主機緩沖區之間的數據交換也是通過中斷響應方式進行的,與通過DMA方式從McBSP讀數據不同,PCI接口工作在猝發方式,其中斷響應函數在輸出緩沖區全部寫滿后將緩沖區內的全部數據寫到主機緩沖區,因此,輸出緩沖區無需分片。采用這種方式可以減少PCI接口讀寫次數,提高數據傳輸效率。

4基于多線程的主機處理技術

DSP數據采集處理系統的處理結果需要輸出到主機,主機可以對處理結果進行進一步處理。主機程序最關鍵的部分是要將主機緩沖區的數據讀出來,再寫到硬盤上的文件中。DSP數據采集處理系統的驅動程序在計算機內存中開辟主機緩沖區,在一臺主機上可以允許多個數據采集處理系統同時工作,這時需要同時開辟多個緩沖區。為保證多個數據采集處理系統同時工作,主機在處理時采用了多線程技術,整個主機處理軟件利用C++Builder開發,在該開發環境下很容易實現多線程處理技術。

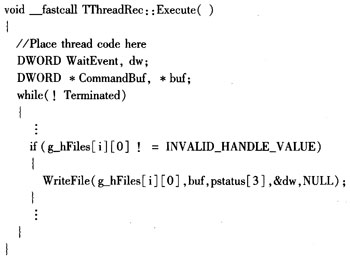

主機處理軟件的核心代碼如下:

從代碼中可以看出,主機多線程處理技術的核心是一個線程執行函數(Execute()),該函數將緩沖區內的數據寫到文件中,在多個數據采集處理系統同時工作時,該處理函數以輪循的方式將對應緩沖區的數據寫入不同的文件句柄(g_hFiles[i][0]),也就是寫入不同的文件,這樣就不會在數據寫入時發生沖突。

主機程序除了將數據寫入指定文件外,還可以控制每一個數據采集處理系統的啟動和停止,并具備在線加載并配置DSP程序的能力,用戶可以通過修改DSP程序的參數來執行不同的處理任務。所有這些功能都是由該系統的硬件驅動程序提供,該硬件驅動程序已封裝成一個庫函數,調用起來較為方便。這樣,用戶就可根據自己的需要開發不同的主機應用程序。

5結束語

基于TMS320C6205的數據采集處理系統已經在實際應用中獲得了良好的效果,特別是該系統可以通過加載不同的DSP處理程序進行不同的數據處理,大大拓展了該系統的應用范圍,充分體現了基于DSP的數據采集處理系統在應用上的靈活性。同時,由于多個采集處理系統可同時工作,整個處理系統可以適合不同應用場合的需要,可以勝任不同處理能力的需要。

評論