高效FPGA乘法器在無線基站中的使用

基于WiMax及其派生標準的新興寬帶無線協議需要越來越高的吞吐量和數據速率。這些協議提出的快速芯片速率和數字射頻處理可以在使用FPGA方案的硬件上得到最佳的實現。

本文引用地址:http://www.j9360.com/article/84431.htmFPGA非常適合作為高性能、高性價比的解決方案來實現這些物理層協議中的數字功能,因為它們包括以下豐富的資源:

1.DSP模塊,可以用來實現各種FIR濾波和FFT/IFFT操作所要求的乘法器和加法器/累加器功能;

2. SERDES收發器,可以支持無線前端與基帶數字板之間的CPRI和OBSAI接口;

3. 重要的FPGA嵌入式RAM塊存儲器(EBR),可以用來存儲濾波器系數,執行塊交錯以及實現FEC解碼(Turbo、維特比、Reed-Solomon等);

4. 高速LVDS I/O,分別支持到DAC和來自ADC的寬并行接口。這些轉換器定義了射頻/模擬功能和廉價數字基帶邏輯之間的界限。接口的速率越高,低成本FPGA解決方案便能集成更多的數字上變頻/數字下變頻功能。

本文重點討論第一種資源,即DSP乘法模塊。通過減少和優化DSP乘法模塊在FFT和FIR中的實現,設計師可以在盡量減少資源使用的條件下滿足吞吐量要求,從而允許用戶使用最具性價比的現成FPGA器件。下面對這四種乘法器節省技術進行介紹。

用于WiMaxOFDM功能的高效復數乘法

WiMax系統設計的一個重要特征是支持正交頻分復用(OFDM)。FPGA使得分別使用IFFT和FFT在離散時間內實現OFDM發送器和接收器變得特別容易。諸如802.16a等協議需要256樣點的FFT。而802.16e這些協議要求多種FFT樣點,或者可以靈活調整的FFT樣點以適應動態信道和帶寬要求(可擴展OFDMA)。

復數乘法

在執行256和1024樣點FFT時,可通過Radix-4結構獲得乘法器的最高效使用。FFT算法通過復用4樣點離散傅里葉變換(DFT)蝶形結構進行分解。例如,一個16點的FFT可以通過按時間抽取、按頻率抽取或其他相關分解方式用2級Radix-4 DFT結構實現。第1級由4個4樣點DFT組成,第2級同樣由4個4點DFT組成。由于每個DFT的輸出要求在饋送給下一級之前為結果提供3個相位因子,因此第1級和第2級之間的9個相位因子需要9次復數乘法。

初看起來,執行一次復數乘法需要4個乘法器和2個加法/減法器。然而,該表達式可以重新寫成另外一種只需3個乘法器、3個加法器和2個減法器的表達式。值得注意的是,加法器是在FPGA的內核邏輯中實現的,使用了豐富的逐位進位模式(ripple mode)的通用可編程邏輯單元(PLC)片。

如果D=Dr+jDi是復數數據,C=Cr+jCi是復數系數,那么復數乘法的標準表達式如下:

E1:R=D*C=(Dr+jDi)*(Cr+jCi)=Rr+jRi (1)

其中Rr=Dr*Cr-Di*Ci, Ri=Dr*Ci+Di*Cr

上述標準表達式要求使用4個乘法器。該表達式可以通過代數方法重新整理為:

E2: Rr=Dr*Cr-Di*Ci (2)

E3: Rr=Dr*Cr-Di*Ci+0 (3)

E4: Rr=Dr*Cr-Di*Ci+(Dr*Ci-Di*Cr)-(Dr*Ci-Di*Cr) (4)

E5: Rr=(Dr*Cr-Dr*Ci+Di*Cr-Di*Ci)+(Dr*Ci-Di*Cr) (5)

復數結果的新表達式是:

E6: Rr=[(Dr+Di)*(Cr-Ci)]+(Dr*Ci-Di*Cr) (3次乘法) (6)

E7: Ri=Dr*Ci+Di*Cr (復用來自Rr的乘積) (7)

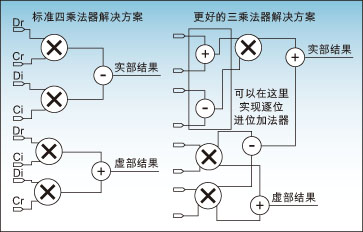

如圖1所示,最優的復數乘法可以用3個乘法器、3個加法器和2個減法器實現。值得注意的是,在FPGA中,加法/減法模塊所用的相對裸片面積要小于18×18的乘法器模塊。

圖1:采用4個和3個乘法器的復數乘法。

總之,所用乘法器數量減少25%可以帶來下面兩大好處之一:

1.在相同FFT吞吐量的條件下可以少用乘法器;

2.在乘法器數量不變的條件下可以提高FFT吞吐量。

數字上變頻/下變頻器中FIR濾波器的高效實現

如下的三個高效乘法器技術可用于實現FPGA中的數字上變頻和下變頻。這已經成為優化的重點領域,因為無線設計師需要滿足將數據從非常高的采樣速率向芯片處理速率轉移的要求。數字下變頻器/上變頻器(DDC/DUC)子系統是基站內發送器/接收器的主要數字器件,以前是用昂貴的模擬/混合信號器件實現的。共有三種技術可以用來減少FPGA實現方案中的乘法器數量。

1.系數對稱的FIR濾波器可節省乘法器;

2.分布式運算操作使用嵌入式塊存儲器;

3.級聯積分梳狀濾波器使用加法器。

評論