基于Modelsim FLI接口的FPGA仿真技術

Modelsim是 Model Technology(Mentor Graphics的子公司)的 HDL 硬件描述語言仿真軟件,可以實現 VHDL, Verilog,以及 VHDL-Verilog 混合設計的仿真。除此之外,Modelsim還能夠與 C 語言一起實現對 HDL 設計文件的協同仿真。同時,相對于大多數的 HDL 仿真軟件來說,Modelsim 在仿真速度上也有明顯優勢。這些特點使 Modelsim 越來越受到 EDA設計者、尤其是 FPGA 設計者的青睞。

Modelsim的 FLI接口(即 Foreign Language InteRFace)提供了C 語言動態鏈接程序與仿真器的接口,可以通過 C 語言編程對設計文件進行輔助仿真。

2、協同仿真系統結構及意義

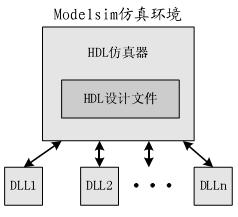

協同仿真就是利用仿真工具提供的外部接口,用其他程序設計語言(非 HDL 語言,如C 語言等)編程,輔助仿真工具進行仿真。Modelsim 提供了與 C 語言的協同仿真接口。以Windows 平臺為例,用戶通過 modelsim提供的 C 語言接口函數編程,生成動態鏈接庫,由modelsim調用這些動態鏈接庫進行輔助仿真(圖 1)。

圖 1協同仿真示意圖

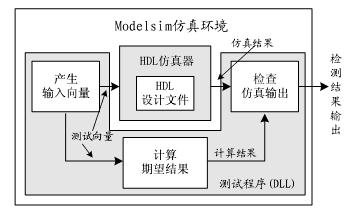

Modelsim 與 C 語言協同仿真一是用于產生測試向量,避免手工編寫測試向量的繁瑣;二是可以根據程序計算結果自動檢查仿真結果正確與否;三是模擬其他模塊(如 RAM)的功能,在系統級對設計文件仿真。實際中一般是把一和二結合在一起,用程序產生仿真向量,一方面輸出給設計文件作為輸入,另一方面由程序本身對該向量計算,把得到的結果與仿真器的輸出結果比較,檢查邏輯是否正確(圖 2)。至于模擬功能,現在已經有一些通用芯片的模擬程序,如 denali 可以模擬 RAM 的功能。另外,用戶也可以利用 modelsim 提供的編程接口自己模擬一些芯片的行為,然后與設計文件連接到一起仿真。

圖 2 語言測試程序對 VHDL 設計的協同仿真結構圖

3、C語言對 VHDL設計的協同仿真

3.1 構成框圖

仿真文件的構成如圖 3 所示,包括 HDL 文件和動態鏈接庫(即 C 程序)。圖中 C 程序對應的 VHDL 文件要負責聲明對應的動態連接庫文件名及初始化函數,另外還可以給出一些調用參數。動態鏈接庫中用到的輸入輸出信號也要在對應的 VHDL 文件中聲明。

圖3 仿真文件構成示意圖

例如,假定有一個DLL文件名為sim.dll,對應的初始化函數為sim_init,有輸入信號in1,in2,輸出信號 out1,out2,可以這樣編寫對應的 VHDL 文件 (sim.vhd):

library ieee;

use ieee.std_logic_1164.all;

entity sim is

port(

in1: in std_logic;

in2: in std_logic;

out1: out std_logic;

out2: out std_logic;

);

end entity sim;

architecture dll of sim is

attribute foreign : string;

attribute foreign of dll : architecture is "sim_init sim.dll”

begin

end;

仿真時,仿真器對頂層的 HDL 文件進行仿真,并根據各 VHDL 文件的動態鏈接庫聲明來調用、執行相應的動態鏈接庫。

3.2 動態鏈接庫的程序結構

modelsim 在仿真時,根據 VHDL 文件的聲明,調用 DLL 文件(如 sim.dll)。在 VHDL文件中已經給出了調用文件(sim.dll)和初始化函數名(如 sim_init),modelsim根據這些信息,調用 sim.dll中的 sim_init 函數,完成初始化工作。初始化包括:

1. 初始化全局變量;

2. 設置 VHDL 輸入輸出信號與 C 程序變量的對應關系;

3. 設置輸出信號的一些初始狀態(mti_ScheduleDriver);

4. 設置在仿真器重新仿真(restart)和仿真器退出仿真(quit)等情況下執行的一些函

數(mti_AddRestartCB 和mti_AddQuitCB 等),如釋放動態申請的內存等等;

5. 設置敏感表,給出在某些信號發生某些變化(如時鐘上升沿等)時執行的函數。

6. 等等。

下面結合 3.1的例子(sim.vhd),給出C 程序的設計步驟。

評論