NiosII多核處理器之間通信技術的研究

引言

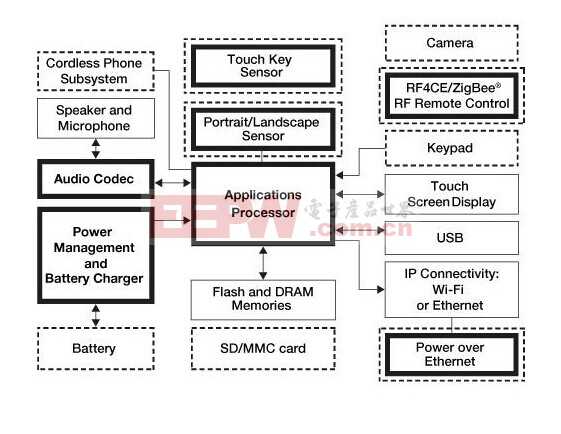

本文引用地址:http://www.j9360.com/article/81623.htm隨著應用領域的擴大,人們對微處理器系統的性能、功耗和成本提出了越來越嚴格的要求。單純依靠提升時鐘的方法已經不能滿足需要,在移動通信、軍事應用、消費電子、智能控制設備等領域,多核處理器的解決方案成為一種主流趨勢。

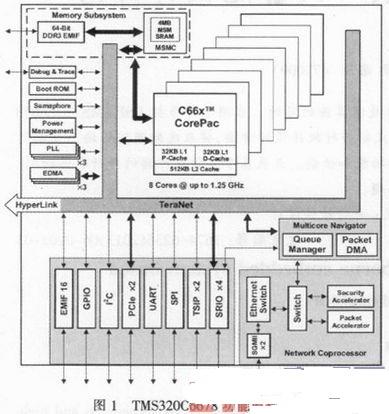

Altera公司在其FPGA中實現的NiosII處理器是一個用戶可配置的通用32位RISC軟核微處理器,Nios II 5.0及其以上版本支持多處理器系統的創建和調試。Nios II多處理器,除了軟核本身超過200DMIPS的高性能之外,Altera開發用于Nios/NiosII處理器的Avalon參數化接口總線具有友好的多主從仲裁能力,可以有效地實現系統資源共享。在清華-Altera聯合實驗室的支持下,筆者對NiosII多核處理器之間共享通信的幾種可行方案進行研究,并且在自行設計的NiosII開發板上完成設計測試驗證,分析比較各種方案的技術特點、優勢與不足,提供給不同系統的應用者參考。

NiosII多核間幾種可行的通信方案

雙口RAM和PIO核的多核中斷通信方案

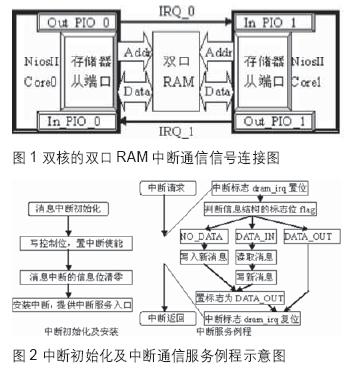

雙處理器可采用一個雙口RAM和中斷信號通過定義某種信息數據結構來進行通信。在NiosII雙處理器系統,可以采用FPGA中實現的片上雙口RAM和通用IO組件PIO核來實現多核中斷通信。通信的中斷信號使用PIO組件產生和接收,雙核通信的連接如圖1所示。由于Avalon總線具有多主從仲裁能力,同一外設可以同時掛載在不同軟核上,有訪問競爭時由總線自己仲裁決定哪個主方取得從設備訪問權,雙口RAM和單口RAM均可以通過Avalon總線掛載在多個NiosII軟核上,二者的區別在于:雙口RAM設備有兩套從端口被Avalon總線當作兩個設備,雙核可以同時對其進行讀操作;單口RAM只有一套從端口被Avalon總線當作一個設備,多核對其的讀寫操作是分時進行的。

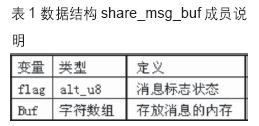

這里設計雙核通過雙口RAM和PIO中斷進行通信的例程。設計信息交換的數據結構share_msg_buf如表1所示。安裝中斷程序及終端服務例程如圖2所示。

通信的關鍵在于消息標志flag狀態的定義:NO_DATA-內存空閑、DATA_IN-有新消息寫入、DATA_OUT-新消息已送出,單個軟核處理器在存儲器空閑(NO_DATA狀態)或者有消息進入(DATA_IN狀態)將新消息讀走之后才能在存儲區寫入新的消息數據;在自己發的消息還未被對方接收(DATA_OUT狀態)時,不做處理,返回繼續等待對方接收消息。標志狀態的定義從軟件上實現了雙核對雙口RAM的互斥訪問,有效防止雙核對共享數據的破壞。這種通信方案經過筆者的NiosII雙核系統驗證測試,消息接收正確。

互斥硬核和共享存儲的多核查詢通信方案

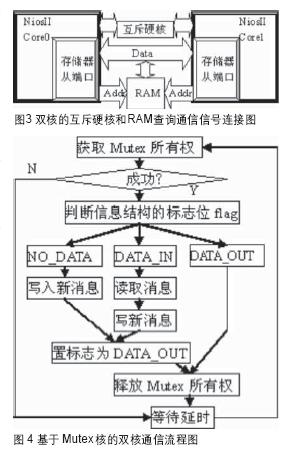

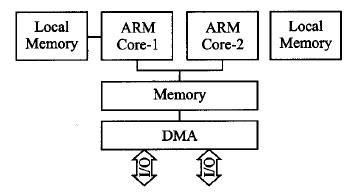

Altera在SOPC Builder工具箱中提供具有Avalon接口的互斥硬核Mutex組件來協調共享資源的訪問。Mutex核提供一個基于硬件的原子測試和置位(test-and-set)操作,允許多處理器環境下決定軟核對Mutex核的使用權,使用Mutex核就可實現多核對相應共享資源(如存儲器)的互斥訪問。這樣多核的通信就可以舍棄雙口RAM,使用片上RAM或者片外存儲器作為共享存儲器,采用查詢方式實現。雙核通信的設備連接如圖3所示,與雙口RAM不同,這里的片上RAM僅作為一個設備掛載到Avalon總線上。

Altera提供NiosII HAL環境下對Mutex核訪問的函數:打開、加鎖、解鎖、判斷Mutex屬主等。使用Mutex核控制片上RAM,單個軟核每次對片上RAM操作之前都要首先取得Mutex核所有權,操作完之后應立即放棄對Mutex核的所有權,避免單個軟核對Mutex核及共享資源的獨占。采用前面表所定義的數據結構作為通信的消息,在查詢方式下,單個軟核需要有任務通過循環不斷檢查共享數據區標志位flag,等待其它軟核送來消息,以便激活自身系統掛起的任務,執行下一步工作。整個流程如圖4所示。

在循環中使用等待延時,避免了多核對Mutex核資源的不停爭用,同時留給處理器一定的消息處理時間,但缺點是延長了通信呼叫和應答的時間,在實時設計中應考慮到延時時長對多核通信的影響。此方案在筆者的NiosII雙核系統工程中通過驗證。

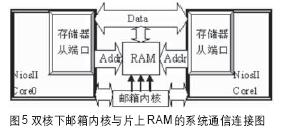

郵箱內核和共享存儲的多核阻塞通信方案

Altera還提供帶Avalon接口的郵箱內核mailbox組件在多核處理器之間發送消息。郵箱內核含有兩個互斥體:一個保證對共享存儲器的唯一寫訪問;另一個保證對共享存儲器的唯一讀訪問,它與獨立共享存儲器一起使用實現多核處理器間的消息隊列通信。郵箱內核適于雙核間單方向的消息通信,功能相當于FIFO緩沖隊列,其傳送的消息往往是指向共享內存塊結構體的指針,代替實際的數據傳輸,提高數據交換效率。該系統連接如圖5所示。

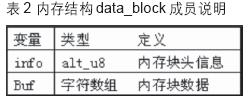

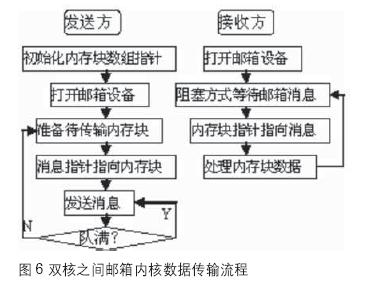

在NiosII HAL環境下對郵箱內核訪問的函數有:打開、關閉、獲取消息、等待消息、發送消息。在構建郵箱內核組件時,選擇可用的共享存儲器作為消息隊列內存,指定消息隊列長度size(不超過存儲器容量)及其在存儲器中的偏移量Offset。這里選擇片上RAM作為共享存儲器,將其分為兩部分:一部分作為消息隊列內存;一部分作為消息指針指向的內存數據結構塊。定義內存數據結構如表2所示,頭信息info可以作為數據幀的序號,保證數據的按序接收。使用郵箱內核消息隊列完成雙核間大量數據傳輸的流程如圖6時進行等待;數據接受方處理器處于等待消息的狀態,一有消息就接收進來。可以在實時操作系統中單獨建立發送數據和接收數據的任務,由于沒有中斷和查詢過程,此方案可以達到單方向很高的數據傳輸率,在筆者的NiosII系統工程中得到了驗證測試。

通用串行接口總線的多核通信方案

在NiosII多核處理器中可以使用通用串行接口總線如UART、SPI、I2C等進行相互間的通信。這些總線有的是NiosII的通用組件在SOPC Builder中直接添加使用,有的可成熟的第三方組件在SOPC Builder中使用。目前NiosII中可用的幾種串行總線如表3所示。

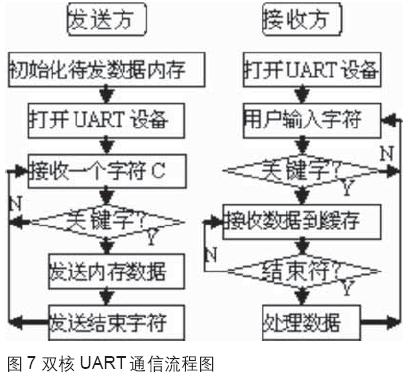

幾種總線各有優缺點和使用限制,例如UART總線比較通用、工作在異步方式,使用方便,但針對一對一的通信,數據率稍低;SPI總線工作在同步方式,一個主設備可以掛多個從設備,數據率較高,但控制比UART復雜、數據線較多。應根據具體應用選擇合適總線。這里以UART總線說明和驗證通用串行接口總線完成多核間通信的方案。UART核是Altera提供的NiosII通用組件,實現了一個簡單的寄存器映像的Avalon從接口,可以很容易集成到NiosII處理器中,允許主外設(如NiosII軟核)通過讀寫寄存器與其進行通信。UART核至少創建Rxd輸入和Txd輸出兩個IO端口,可根據需要創建CTS輸入和RTS輸出兩個流控信號。這里為每個NiosII軟核創建一個無流控波特率為1.152Mbps的UART組件,其發送端口Txd與另外一方的接收Rxd連接。NiosII HAL提供UART系統庫驅動程序,可使用ANSC C標準函數或者UNIX風格IO函數訪問UART,雙核通信流程如圖7所示。

雙核中的數據發送方查詢監測輸入字符,出現關鍵字時發送數據,并以結束符結束發送;數據接收方等待用戶輸入字符命令,如果是關鍵字則開始接收數據,在收到結束符時結束接收,處理數據。這個方案實現的是數據接收方請求發送,在筆者NiosII系統工程中以1.152Mbps傳輸大數據量,驗證測試沒有問題。也可以根據實際需要使用其它方案。

PIO核自定義協議的多核通信方案

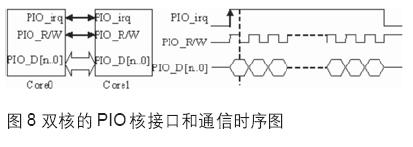

Altera為NiosII提供并行輸入/輸出PIO核,在Avalon從端口和通用I/O端口之間建立存儲器映像接口,PIO組件可配置為輸入、輸出、輸入輸出、雙向三態四種類型,其中后三種類型可提供信號邊沿捕獲(Edge Capture)和中斷請求。利用PIO并口可將雙核連接起來,定義自己的接口形式和通信訪問協議進行通信。雙核間的互連使用的是FPGA片上邏輯,不占用FPGA的IO引腳,寬度最高32位,同等數據率下效率大大高于串行總線,可使用中斷、查詢或者二者相結合方式進行通信。這里定義一種PIO通信接口和時序如圖8所示。

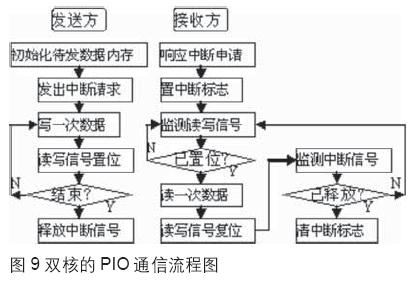

在中斷信號PIO_irq的上升沿提出中斷申請,啟動一次通信,數據傳輸方將讀寫標志信號PIO_R/W置高,同時向數據線PIO_D寫入數據;數據接收方在相應中斷信號后,檢測到PIO_R/W信號變高,則讀數據線PIO_D獲取數據,同時將PIO_R/W置低表明數據已讀,可以進行下次數據傳送。數據傳輸方通過將PIO_irq信號置低表明完成一次通信,數據接收方檢測到PIO_irq信號為低時停止本次通信。這種中斷和查詢相結合的方案效率很高,任意一方都可以發起通信,通信的速率取決于NiosII軟核對端口讀寫延時和數據的處理速度或者寫數據緩沖區的速度。軟件通信流程如圖9所示。

結語

表4對上述各種方案進行了一下比較,分析了每種方案的特點和適用范圍。

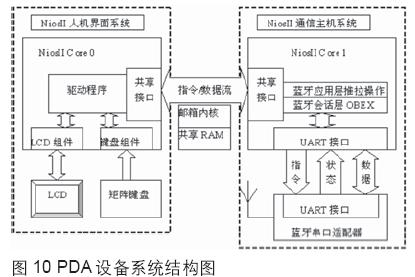

筆者的PDA考評系統項目采用了NiosII雙核設計,使用方案三(郵箱內核和共享存儲的多核阻塞通信方案)完成雙核間的通信。PDA設備作為實驗考評系統的客戶端,通過藍牙無線通信與建有學生課程成績數據庫的服務器進行通信,實現實驗現場學生成績的查詢、修改、數據文件的傳輸等功能,系統的功能結構如圖10所示。NiosII雙核分為兩個系統:(1)NiosII人機界面系統。負責管理矩陣鍵盤按鍵和LCD顯示界面的驅動;(2)NiosII通信主機系統。實現完整的藍牙協議棧,完成與數據庫服務器進行通信的任務。雙核之間鍵盤操作指令和LCD顯示數據的交換通過上文所述的方案三——郵箱內核和共享存儲的方式實現。

NiosII多核處理器在FPGA中易于實現,并且多核之間通信可選方案較多,適應范圍廣,相信會在越來越多的系統中采用。

參考文獻:

1. Altera Corp. QuartusII Version6.1 Handbook. Altera. 2006

2. Altera Corp. Creating Multiprocessor NiosII System Tutorial. Altera. 2005

3. Altera Corp. NiosII Processor Reference Handbook. Altera. 2005

4. Altera Corp. NiosII Software Developer’s Handbook. Altera. 2005

5. Altera Corp. Avalon Interface Specification. Altera. 2005

數字通信相關文章:數字通信原理

通信相關文章:通信原理

存儲器相關文章:存儲器原理

加速度計相關文章:加速度計原理

評論