一種精度可調的數字控制移相原理

1 引 言

本文引用地址:http://www.j9360.com/article/77955.htm移相電路在現代通訊技術、波形調制和雷達掃描等許多方面有著大量的運用。目前實現方式大致可分為模擬和數字2類。模擬移相器的電路較為復雜、線性差、響應時間慢,抗電磁干擾能力差。而數字移相器主要分2類[1]:第一類是運用直接數字式頻率合成技術DDS。另一類是利用單片機計數延時的方法實現。其中使用DDS的移相器的實現精度大多依照"360°/2°"的方式實現,即其能夠實現180°,90°,45°,22.5°,11.25°等精度[2]。另外其實現電路也較為復雜;而第二類利用單片機雖然可以實現較高精度的移相,但使用的單片機屬于硬核IP[2],在大規模集成和使用權問題上十分不方便。本文介紹的基于可編程數字控制方法的移相原理,其精度可以通過精度控制輸入信號任意賦予(在本文中精度調制為1°來說明)。此原理的電路采用采樣電路和精度為1°的360倍倍頻器等進行延時輸出波形,方法簡便,電路結構簡單,能夠配合任意工藝特性加以實現,且能夠方便地集成到大規模電路中去。

2 基本原理

本系統是基于數字倍頻器進行延時操作而實現的移相。實現原理是把輸入模擬波形(如正弦信號)的周期Tin轉化為原來的1/data,Tin/data即為移相精度,data值通過精度控制輸入信號賦值。當data為360時,精度為1°;當data為720時,精度為0.5°;若要更小的精度,可依此類推。本文中為便于顯示移相波形,把精度設置為1°。則精度為Tin/360,所用的倍頻器倍頻因子即為360。這樣經n個Tin/360延時(n為移相的具體數值,由記時控制輸入信號D賦值),再輸出波形。和原波形相比就形成了移相。從實現的電路方面來講,要把輸入波形周期變為原來的1/360,或者說把輸入波形的頻率變為原來的360倍,最直接的辦法就是采用倍頻器。而數字倍頻器的輸入是數字信號,則應先把模擬量轉化為數字量,這就需要一個模擬比較器。在得到倍頻輸出信號后,為了要得到希望的n值,還應在倍頻器后添加數字定時輸出計數器,以輸出延時控制信號。最后把模擬信號輸入A/D電路,通過ROM存儲,再在延時控制信號的作用下延時輸出數字量,再經過D/A電路還原為模擬量,最終實現移相操作。其中倍頻器具有360倍倍頻能力。

輸入模擬信號(如正弦波)經過信號比較器,波形電壓與零伏比較后,高于零伏的電壓段轉化為高電平,低于的轉化為低電平,這樣輸入信號就轉化為周期相同的數字信號。A/D,ROM,D/A和一些控制電路構成移相輸出控制模塊。其中移相控制部分的倍頻器,定時輸出計數器構成可編程數字控制部分,都可以通過硬件語言編譯實現。這樣得到的系統硬件原理框圖如圖1所示。

以下著重說明數字倍頻器、數字定時輸出計數器和數模混合輸出控制電路。

2.1數字倍頻器

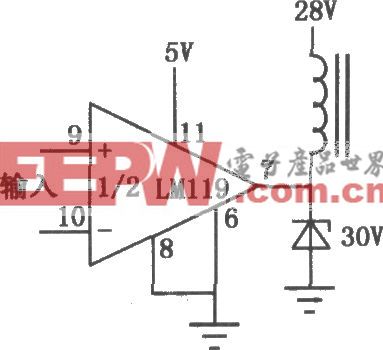

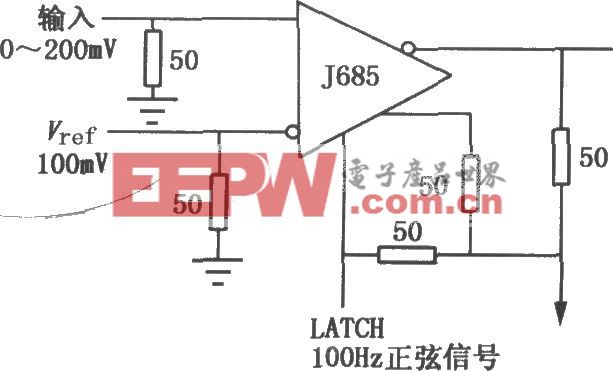

這里使用的數字倍頻器(電路如圖2所示)的算法是基于采樣的原理來實現[4],理論上能夠實現任意倍倍頻,這里為方便說明和顯示波形,設置為360倍,即倍頻因子為360,精度為1°。

當信號A經過比較器后,A轉化為具有相同周期的數字信號DA,他們的周期均為Tclk_in。通過引入高頻時鐘信號(其周期為Thf_clk)采樣,以此來計數在一個Tclk_in中含有的Thf_clk的個數,把這個結果記為Nhf。則有:

Nhf=Tclk_in/Thf_clk (1)

由于倍頻因子是360,所以對于倍頻后的結果clk_div_n1有:

Nhf_of_clk_dive_n1=Nhf/360 (2)

Tclk_div_n1=Nhf_of_clk_dive_n1×Thf_clk (3)

Tclk_div_n1為倍頻后倍頻器輸出波形的周期,Nhf_of_clk_dive_n1為一個Tclk_div_n1中含有的采樣信號周期的個數。

聯立式(1),(2),(3),可得:

Tclk_div_n1=Tclk_in/360 (4)

亦即:

fclk_in×360=fclk_div_n1 (5)

從而實現了360倍倍頻。Tclk_div_n1就是信號A相移27π/360(即1°)時所占的時間間隔。圖3是本倍頻器的仿真波形(這里把倍頻因子固定為360)。在每次輸入信號周期變化后,都按照新的周期進行360倍倍頻

這里應說明的幾點是:

(1)如圖2所示,data就是精度控制信號,不難看出,實際上他也就是倍頻器的倍頻因子。當data=360時,移相精度為1°。那么當倍頻因子改變時,移相精度隨之而改變。若data為720,則移相精度為0.5°;若data為3 600,則移相精度為0.1°。這些都可以通過改變精度控制信號data來實現,從而達到精度可變的目的。

(2)reset為復位信號,在輸入信號DA(也就是電路圖中信號clk_in)時應先復位。

(3)從圖3可以看到,每隔一個Tclk_in,Nhf就會被重新計算一次,并與上次的結果作比較,這樣輸出信號cal_dif會在輸入信號clk_in的周期發生變化時(也就是兩個Nhf數值不一樣時),輸出一個高電頻。這個高電頻就是下兩個模塊數字定時輸出計數器和數模混合輸出控制電路中一部分模塊的復位信號,從而達到倍頻器輸出信號周期自調節的目的。

(4)式(1)~式(5)的推導實際上都忽略了除法中的余數問題。當式(1)除不盡時要考慮余數的四舍五入問題。式(2),式(4)應修改為:

Nhf_of_clk_dive_n1=Nhf/360 (6)

Tclk_in=360×Tclk_div_n1+R (7)

其中,R為倍頻后的時間余數,RN是倍頻后的計數整數的余數,他們是同一概念的2種表述.對余數四舍五入的實現方式是先把Tclk_div_n1作二倍頻處理得到Tclk_div_n2。以Tclk_div_n2對輸入周期Tclk_in再次采樣后得到值N。按照理想無余數的情況考慮,N應該是720。但當余數存在的情況下,若N大于720,則說明,RN≥0.5。那么表示倍頻器的輸出結果Tclk_div_n1的式(3)應修改為:

Tclk_div_n1=(Nhf_of_clk_dive_n1+RN)×Thf_clk (8)

當RN≥0.5時,按四舍五入考慮,可得:

Tclk_div_n1=(Nhf_of_clk_dive_n1+1)×Thf_clk (9)

若N沒有大于720,則說明RN<0.5。那么就按照式(3)處理;否則應該按照式(9)處理。

2.2 定時輸出計數器

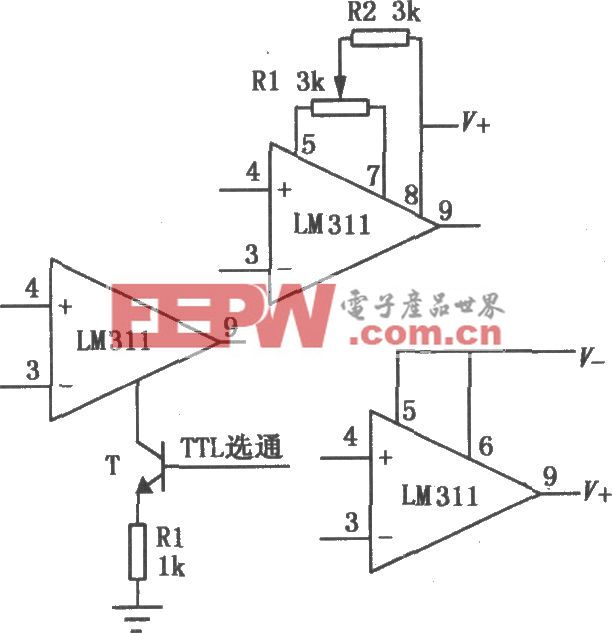

定時輸出計數器的輸入有計數數據data(9位)、復位信號set、數據輸入加載信號q和clk,輸出out.其中clk接倍頻器輸出信號clk_div_n1。定時輸出計數器的仿真波形如圖4所示。計數器的復位分2種情況;首先是倍頻器的輸出信號cal_dif引起的復位;然后在輸入新的數據data時,由q引起的復位。由于數據data是9位,則僅當D<101101000(即10進制的360)時,q才引起復位。否則不復位,數據也不加載。當計數器復位后,out為0,在data個周期后,out輸出高電平。如仿真波形圖4所示,每輸入一個小于360的數,則輸出信號變為低電平,直到延遲時間結束后輸出高電平。

2.3輸出控制模塊

輸出控制模塊的主要作用是波形保持。先保持兩組波形一致,即先在模擬輸入信號輸入A/D[5,6]轉換電路后,得到的數字量同時輸入到兩個相同的ROM中存儲。在這個過程中倍頻器一直處于復位狀態。在ROM中存儲完一個輸入信號局期后,給一個信號使倍頻器停止復位,開始正常工作。ROM1在計數器開始運作時就開始循環輸出數據。ROM2在響應完延時信號后循環輸出數據。其原理框圖如下:

3 最終仿真波形

這里的A/D電路是10位逐次逼近型電路,輸入信號周期為720 μs,時鐘工作頻率為5 MHz,每隔11個時鐘周期采一次樣。應根據采樣的次數確定ROM的大小。這里的輸入模擬信號周期為720μs,A/D時鐘周期為0.2μs,共采樣300次,每次10位數,則這里需要4 k的兩個ROM。ROM2的輸出由定時輸出計數器控制。這里假設相移要求為17°,則其時間延遲Tdelay=17×Tclk_div_n1。最終仿真波形如圖6,圖7所示。

圖7是圖6左下角數據的放大。這是由Cadence 公司的仿真軟件Spectre仿真計算得到。在圖6中,上面的波形為原來的正弦輸入信號;中間的是不經過移相而直接輸出的結果;下面的是移相后的波形。由軟件顯示計算2個波形的時間差為:TB-TA=38.9066μs-4.90673μs=33.999 9μs△34 μs。根據本文介紹的延時控制理論,延時的數值應為:TDelay=17×(720μs/360)=34μs。由此可見,仿真后得到數據和理論數據完全吻合,從而證實了本文原理的正確性。

4 結 語

通過上面論證,文中移相器的精度理論上可以任意定義。倍頻器在因溫度等外界因素導致輸入信號A的周期發生變化時,能立刻自我調整,使輸出與輸入的關系恒定(即fclk_in×360=fclk_div_n1),并能夠根據外部輸入信號A的周期變化進行自我調節適應,另外對倍頻后的時間余數進行了四舍五入處理,因而具有精度高,失真度小的特點。如果調整工藝,并使用性能較高的比較器,那么還可以使得移相器的輸入信號頻率大大提高,從而滿足高頻電路的移相需要,拓寬了應用領域。同時本移相器除了適合正弦信號外,還適用于三角波信號和其他模擬信號的移相。

模擬信號相關文章:什么是模擬信號

比較器相關文章:比較器工作原理

塵埃粒子計數器相關文章:塵埃粒子計數器原理 數字濾波器相關文章:數字濾波器原理

評論