IP技術的深層次變革

——

RevoluTionary IP

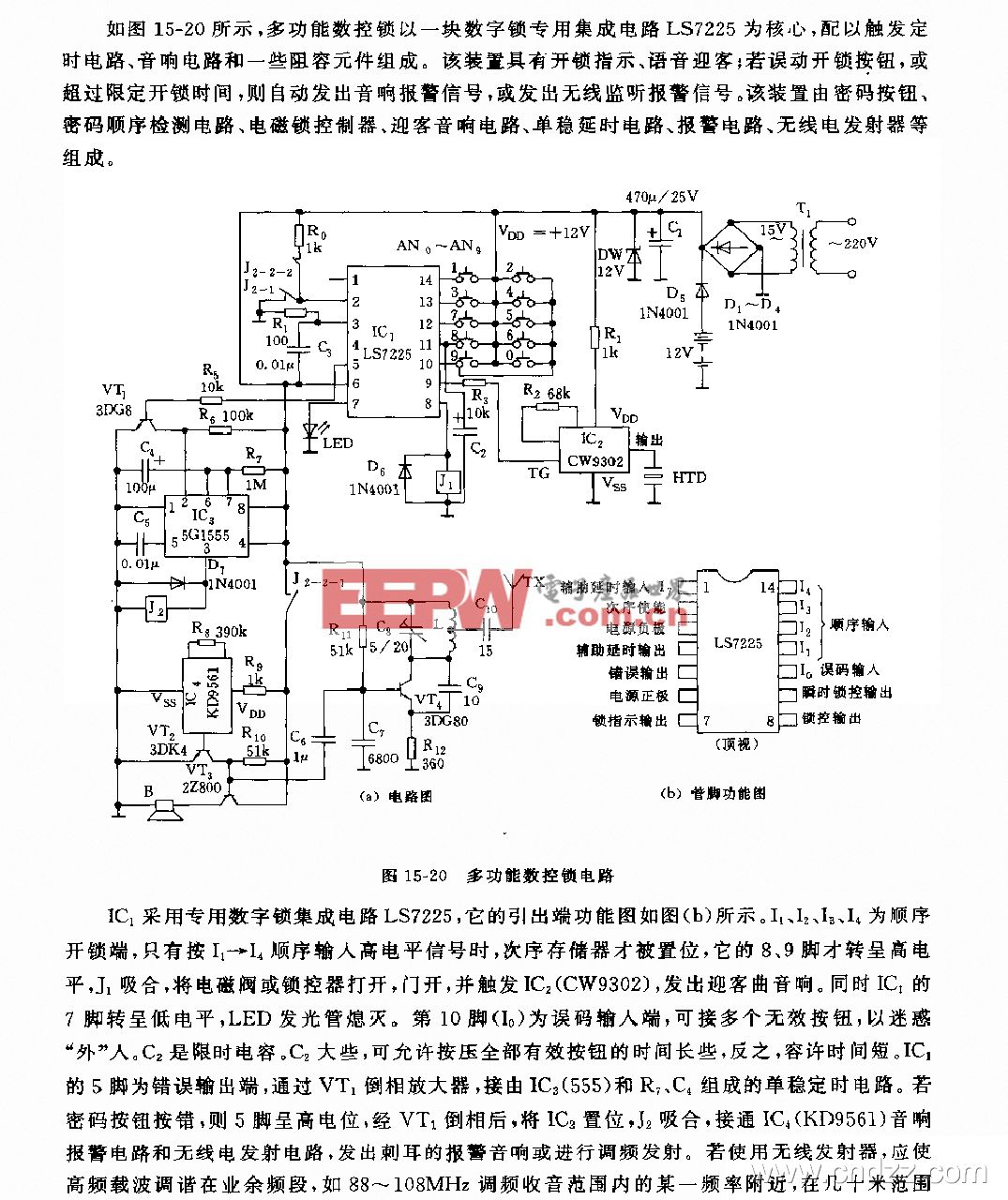

單個芯片上晶體管數量的無休止增加必然導致設計生產率需求的無休止增加。十分顯然,彌補設計生產率不足,充分利用已有的晶體管技術,不能單憑自己來設計每項任務,唯一的方法是使用可靠的供應商提供的IP,事實上,它們確實是完全可以勝任的。

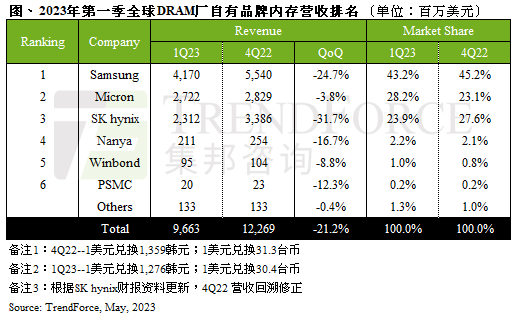

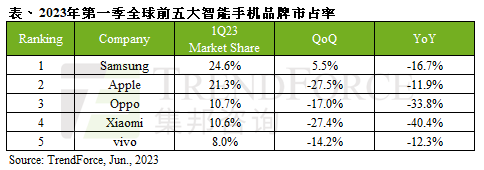

這種情況任何時候不能立即改變。來自IBS的最新數據表明:在典型的130nm芯片中,86%非存儲類晶體管是可重復使用的,也就是說,它們來自因特網或來自第三方IP。IBS還預測,對90nm芯片、這個數字將增加到92%。因此,盡管半導體行業處處不景氣,IP業務卻在持續地增長,2004年IP市場增長22%,為13億美元;而到2007年,能進一步上升至25億美元。

微處理器芯核仍然占據著IP市場的最大份額,約為總收益的四分之一。當芯片公司關注芯核的功利性,利用寶貴的工程資源來創建自己個性化SoC設計元件時,IP的重要性與日俱增。這種趨勢對標準基IP來說也是一個好的兆頭:設計人員認識到,自己設計PCI Express(PCIe)接口將得不償失,要是生產的接口是屬于子標準的,或更確切地說是非標準的,損失更是巨大。

目前,多數出售的標準基IP支持互連,外部總線標準有PCIe、USB2.0、USB OTG、SATA、Ethernet以及IEEE1394/Firewire等,芯片內總線諸如事實上標準AMBA互連技術。從設計者的立場,由于標準日趨復雜,需要具備專業知識,因此使用IP意義重大。業界已證明十分有效的硅IP可以節省寶貴的時間和精力,又可避免不必要的風險。

不僅如此,由于互連技術隱含標準的合格性,購買者需擁有一個功能基準測試程序,用它來測試標準的質量,即是否依從相關機構制定的標準。這里,標準以及管理標準機構的實力是關鍵。例如,USB標識符通過互操作性推行批量驗收是最有效的。合格性的壓力始于消費者,經過經銷商,最終落在IP供應商頭上。成功的標準基IP生產商通常積極參與標準機構的活動,以便標準一旦通過和公布后,能及早地產生IP解決方案。例如PCI-SIG通過PCIe標準后,Synopsys Desigh Ware PCI Express Endpoint芯核就被列入第一批產品合格的清單中。此外,Dsign Ware PCIe IP可向規范測試卡供電,公司可用該卡來測試規范的合格性。

表面看來,進入標準基IP領域的門檻并不高,事實上,提供這類有利可圖的IP是很困難的。提供設計人員期盼的高質量和合格的標準需要投入居大的資金,而市場只認可合理的標準基IP價格。只有具備開展這類研發活動豐富的資源和工具,以及有廣泛的客戶基礎來削減成本的公司,才能在標準基IP市場中取得成功。

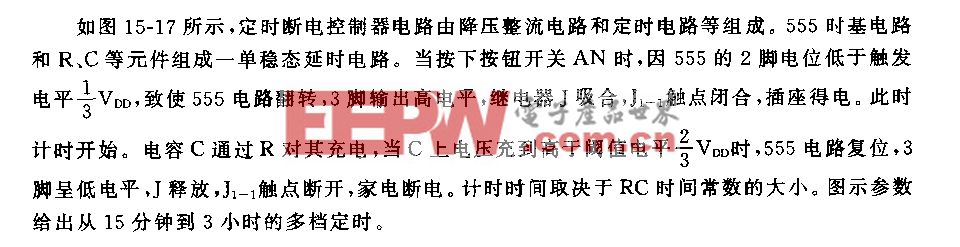

標準基領域的IP不限于數字IP和模擬IP。事實上, 一個重要的和正在迅速崛起的領域是混合信號物理層(PHY),用于高速串行接口的數字芯核和外部世界的互連。設計人員期待標準接口供應商提供數字和混合信號芯核以及驗證IP(VIP)的完整解決方案。PHY采取在特定工藝技術中實施的硬IP形式;而VIP功能塊是經過充分測試的行業標準總線和規范的模擬模型,用標準和規范的產生和響應來驗證規范條例的合格性。設計人員需要的正是這種完整的、可重配置的子系統,即多個IP芯核和片上互連總線,它們組合在一起就有可能讓設計人員在增添自己的個性化的功能塊后,重新創建可重復使用的專用平臺(圖1)

近代芯片研發遵循這樣的原則,將一個簡單的產品轉化為一系列較復雜的實施單元過程。很多設計人員習慣上把驗證任務看成是第一階段RTL代碼已經完成后的事。然而,最成功的實例表明,驗證應始終貫穿在每一個研發階段。VIP塊作為驗證中基準測試程序一部分,和可實施的IP一樣,能縮短系統驗證時間,并提高產品的質量。因此,當設計人員樂于使用第三方IP時,他們開始要求,供應商也開始提供更高質量的、與驗證技術相結合的IP。

多數旨在ASIC設計的設計人員在很多場合是以FPGA實現ASIC設計的。這就意味著,其IP解決方案,包括在功能塊上和子系統/平臺級上,除了支持至ASIC設計的自動路徑,還要支持至FPGA的自動路徑。不然他們會發現,在FPGA中測試的和在ASIC中測試的根本不是一回事。同樣,以FPGA為對象的設計人員,如果想確保大批量生產獲得成功,亦應以重新以ASIC為對象進行設計。

當前設計人員,為了節省采購時間,簡化業務合同,減少管理工作量,總想從少數供應商處獲得盡可能多的IP。越來越多的芯片公司只向少許幾個可靠的供應商購買整個IP公文包,讓設計人員迅速而又方便地得到一整套可互操作的IP。事實上,在這方面供應商和芯片商之間的關系正在演化成真正的合作伙伴關系。當IP市場中供應商更加成熟時,這種聯盟的威力也影響到IP供應商。IP供應商主要有下列5家:ARM、Rambus、Synopsys,TTPcom和Artisan,每家公司都有自己的優勢產品,占據著不同的市場份額。

Synopsys最新一項調查表明,當前,超過20%的設計人員在他們每個芯片中使用的IP塊不少于6個。公司想降低風險和成本,提高生產率,IP是解決方案的關鍵部分。但是,為了充分挖掘潛力,設計人員應慎重地選擇標準基IP和外部的“star”IP兩種產品,不僅要詳察其IP質量,還要詳察保證質量方法、互可操作IP公文包、IP集成在子系統上自動化路徑方案,以及設計人員所需的供應商全方位、專業化的支持能力。(東華)

圖1 創建可重復使用的專用平臺

評論