SoC設計:利用SoC互聯IP來增強物理布局

Arteris,讓人聯想起arteries(動脈)。顧名思義,該公司要做SoC中IP和功能塊之間互聯的動脈。2013年筆者就采訪過這家年輕的初創公司,市場副總裁Kurt Shuler的生動講演就給筆者留下過深刻印象,他提出了NoC(Network on a Chip)概念,這當然不是網絡芯片的意思,而是一種在SoC內部加速IP和各功能塊之間互聯的IP。之所以叫NoC,因為該公司的創始人過去是網絡出身,認為可以把網絡概念移植到芯片上。

本文引用地址:http://www.j9360.com/article/284667.htm

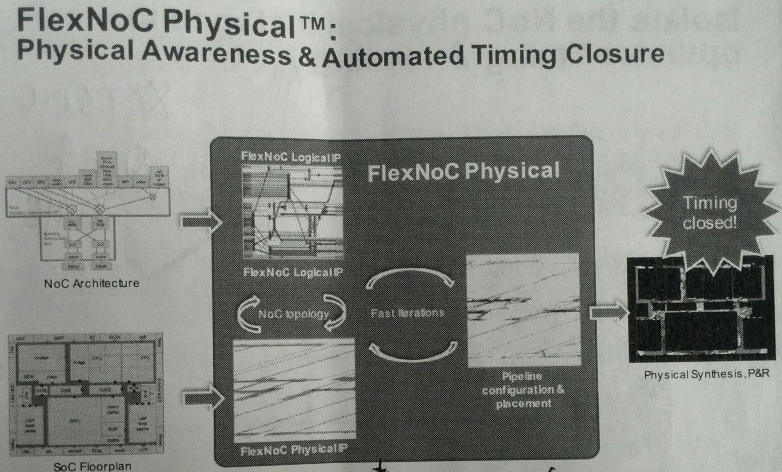

在2015年Globalpress公司舉辦的Euroasia Press’ tour(歐亞媒體赴美采訪團)上,Arteris又帶來了哪些新特色?Kurt稱在其NoC互聯上增加了物理意識(awareness)。

FlexNoC好在哪兒?

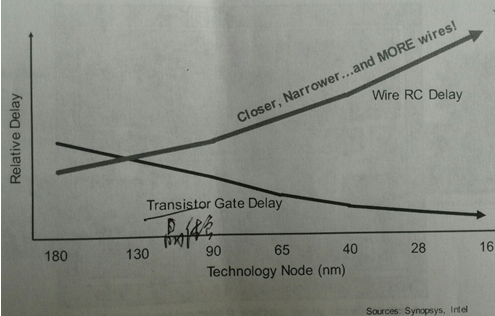

一句話,FlexNoC解決了布局布線的問題。一般地,芯片越小電阻越大,距離更近更容易引起信號干擾,更多的晶體管意味著更多的連線。通過可視化的拓撲俯視圖, Arteris IP——FlexNoC自動產生一個架構來優化時序和布線(routing)。

具體地,FlexNoC的互聯有三類:FlexNoC工具,FlexNoC庫和SoC系統特性。

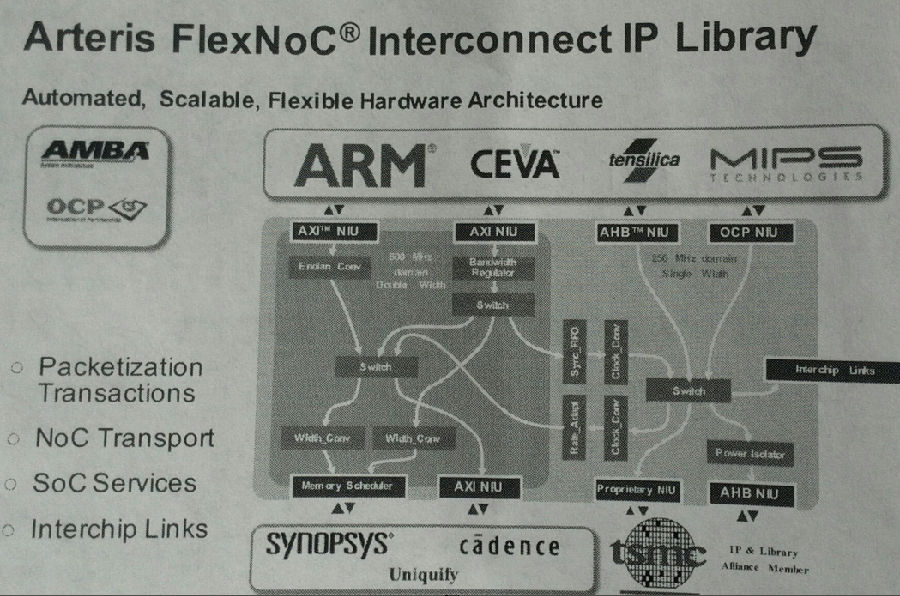

其中,FlexNoC互聯IP庫的特點是自動、可擴展、靈活的硬件架構(如下圖)。可實現打包交易、NoC傳輸,提供SoC服務、芯片間連接等。使IP處理器核廠商ARM、CEVA、Tensilica、MIPS,與EDA工具廠商和代工廠商順利對接。

28nm及以下的物理互聯IP挑戰是:1.架構需要SoC拓撲的可視化物理影響,2.TL(晶體管邏輯)工程師需要花費數月手工增加管線(pipeline),3.布局工程師得到的互聯IP RTL不是物理驗證的。

為什么互聯如此重要?看看下圖的線RC與門延遲之間的鴻溝就可知曉。

SoC IP的布局圖大概如下所示。如此復雜,不可能用一個時鐘周期走完一個28nm SoC。因為物理距離決定這些管線的數量。例如,NoC在時鐘600MHz=1.67ns循環時間時,可用時間是1.42ns;傳輸延遲0.644ns/mm(最好在28nm、TSMC 28HPM工藝時);管線-管線最大距離是2.2mm。

新的FlexNoC Physical的特點是:具有物理意識與自動時序收斂。1.采用自動化的管線插入,可以節省1~3個月的迭代時間;2.節省10%~15%的互聯面積,而不必用過度設計(overdesign)的方法,產生額外的管線數量。3.節省2~4個重要的延遲循環,方法是通過匹配時序目標來實現每個NoC IP,而不是過度設計。4.給布局過程提供的一個更好的起點,來減少布局循環和提高布線的效率。

據悉,TI、三星、Altera和華為海思等是Arteris FlexNoC的客戶。

評論