局部應變技術可望提高FDSOI性能

法國研究機構CEA-Leti宣布開發出可為全耗盡型絕緣體上覆矽(FDSOI)矽通道制程誘導局部應變的2種新技術,可望用于實現更快速、低功耗與高性能的下一代FDSOI電路。

本文引用地址:http://www.j9360.com/article/284533.htm意法半導體(STMicroelectronics;ST)和Globalfoundries倡議為先進晶片中采用FDSOI,并視其為能夠達到世界級能效的方法,而且不必面對像FinFET制程的復雜性與高成本。

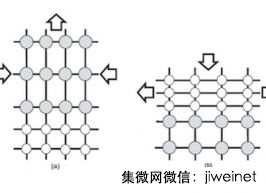

晶格上的應變通常用于增加傳統平面CMOS與FinFET CMOS的行動性。如今,Leti則提議將它用在下一代的FDSOI電路上,以實現同樣的好處;使其得以在相同的功耗下實現更高性能。

無論是FinFET或FDSOI制程都十分重要,因為在FDSOI中的 p-通道FET需要矽鍺(SiGe)通道材料的壓縮應變,同時也需要拉伸應變來改善矽晶n-通道 FET。Leti分為為兩種制程開發新技術,使其能在MOSFET通道中誘導高達1.6GPa的局部應變。

LETI表示,由于28nm FDSOI并不一定需要應變,這兩項技術主要瞄準的是22/20nm節點。第一種技術利用從SOI薄膜頂上的松散SiGe轉移應變。這可用于提高短通道電遷移率達到20%以上。

第二技種技術取決于高溫退火下的埋層氧化物潛變至插入覆晶中的拉伸應變。Leti指出,這種潛變也可以用于導入壓縮應變。

這種應變通道可增加CMOS電晶體的導通電流,以及在相同功率時實現更高的性能,或在一定性能時降低功耗。

評論