多核嵌入式系統的節能機遇與策略

本文列舉了多核嵌入式系統存在的一些主要局限,并對解決這些局限的可行方案進行了探討。將以一些嵌入式系統為例,指出利用現有架構改進系統節能效果的機遇。多核處理器與新興的嵌入式平臺的結合能夠滿足現代嵌入式應用所需的高計算能力。但是,此類嵌入式應用需要進行高頻切換,這將導致功耗較大、芯片溫度過高,以及電源接地噪聲。開發人員可以通過本文找出改進現代嵌入式系統節能效果的機會,并了解實現電源效率最大化的可行方案。

本文引用地址:http://www.j9360.com/article/274627.htm多核處理器的自主節能

本文以甲骨文(Oracle)/SunMicrosystem公司的UltraSPARC T1處理器為例展開論述。選擇UltraSPARC T1的原因是,其設計源代碼、仿真工具及設計驗證套件均為開源,而且可以從Oracle公司網站上下載。本文將利用此案例討論從哪方面以及通過何種方式實現節能。

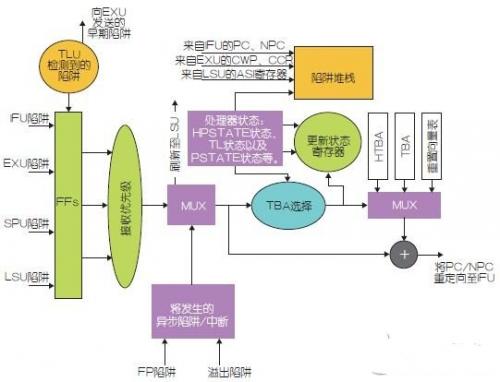

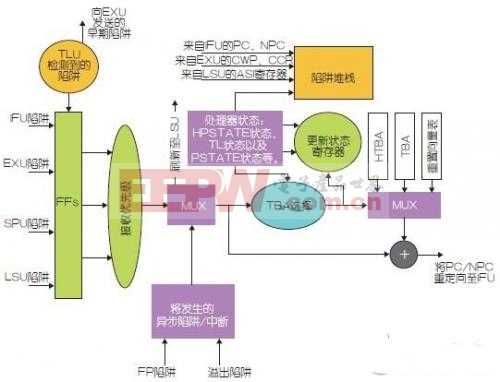

圖1顯示了與處理器每個內核相關的陷阱邏輯單元。陷阱實現了軟件從低級到高級特權模式(例如從用戶模式到管理或監督模式)的控制矢量傳遞。就UltraSPARC T1處理器而言,Tcc指令以及因指令引起的異常、復位、異步錯誤或中斷請求均會導致陷阱的發生。

圖1:陷阱邏輯單元

通常,陷阱會導致SPARC流水線被沖刷(Flush)。處理器狀態將被存儲在陷阱寄存器堆棧中,而陷阱處理程序代碼則將被執行。控制的實際傳遞是通過含有每個陷阱處理程序前八個指令的陷阱表來實現的。用于將陷阱傳遞到特權模式中的表格的虛擬基址在陷阱基址(TBA)寄存器中被指定。表格中的位移則取決于陷阱的類型和當前的陷阱級別。當遇到DONE(完成)或RETRY(重試)指令時,陷阱處理程序代碼執行完畢。陷阱可能與SPARC內核流水線同步或異步。圖2顯示了與SPARC內核其他硬件模塊相關的TLU中的陷阱控制和數據流。從IFU、EXU、LSU及TLU傳入的陷阱的優先級最先被解析,解析的陷阱類型被確定。根據陷阱類型,以及在隊列中沒有其他更高優先級的中斷或異步陷阱待處理的情況下,系統將向LSU發送沖刷信號,以提交之前未完成的所有命令。此外,陷阱類型也決定了什么樣的處理器狀態寄存器需要被存儲到陷阱寄存器堆棧中。之后,將選擇陷阱基址并將其發往流水線做進一步執行。

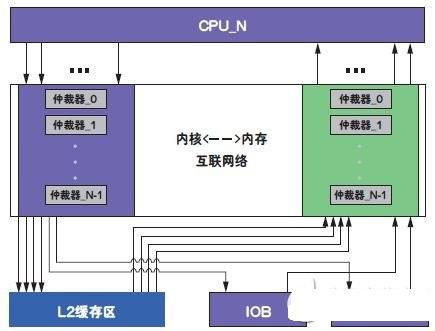

圖2:芯片框圖

圖2顯示了多核嵌入式處理器的芯片布局。該處理器有可變數量的內核、L2緩存體(bank)、內核外浮點單元(FPU)及輸入輸出邏輯,而且它們通過芯片上的網絡互連。在CASPER仿真環境中,設計師可以對各種架構參數進行修改。

節能機遇

對于上述多核嵌入式處理器,已確定了以下內核級和芯片級節能候選元素(PSC):

1.寄存器文件,即線程專用單元。每個線程都有一個160雙字(64位)的寄存器文件,而且當線程的某個任務被阻塞或空轉時可以節省大量功耗。

2.數據緩存未命中時,用以排列數據的加載未命中隊列(LMQ)。線程之間可以共享加載未命中隊列,但通過這種方法節省的功耗較少。

3.分支預測器。分支歷史表可以是線程專用的,因此可以節省大量功耗。

4.當內核中所有線程的所有任務發生阻塞或空閑時,或沒有任務被調度到內核中的任何線程時,整個內核可以節省大量功耗。

5.內核中用于硬件和軟件中斷的陷阱單元。研究結果顯示,在UltraSPARC T1處理器中,用于典型SPECJBB網絡處理應用的陷阱指令在所有指令中所占的百分比還不到1%.這表明,陷阱單元是非常好的潛在節能元素。請注意,雖然在大部分時間內其余的陷阱邏輯可能處在節能模式下,接收陷阱的輸入接收隊列需一直保持在活躍狀態,但隊列的功耗可以忽略不計。

6.在緩存體和輸入輸出緩沖器之間控制數據流的用于L2緩存的DMA控制器。

7.內核和L2緩存體之間的命令和數據隊列。

8.當需要訪問片外緩存或主存儲器時,只有在片上L2緩存有緩存未命中時才會被激活的緩存未命中路徑邏輯。

矢量控制相關文章:矢量控制原理

評論