LEON處理器的開發應用技術文獻及案例匯總

LEON是一款32位RISC處理器,支持SPARC V8指令集,由歐洲航天總局旗下的Gaisler Research開發、維護,目的是擺脫歐空局對美國航天級處理器的依賴。LEON的主要產品線包括Leon2、Leon3、Leon4。

本文引用地址:http://www.j9360.com/article/273882.htm本文采用局部熵邊緣檢測算法,將圖像采集,邊緣檢測和圖像顯示三個部分封裝設計為IP(Intellectual Property)核,通過AMBA APB總線嵌入到LEON3的經典SoC架構中。實現了多路數據并行處理和DSP模塊加速處理,配合CPU軟核的協調參數配置功能,可以充分發揮硬件設計的高速性和靈活性。

本文就介紹了LEON2微處理器核,快速的建立起一個SOC的平臺的原型對于驗證系統性能與加快軟件開發都是相當重要的。本文還詳細闡述了如何在Altera的FPGA開發板上建立基于LEON2微處理器的SOC原型平臺。

本文將從Leon2的結構、技術特點、軟硬件的開發過程和應用實例等四個方面進行介紹。在技術特點中,主要介紹了它所遵循的SPARCV8規范、采用的AMBH2.0內部系統總線協議、容錯設計方法和VHDL編程風格等。

本文結合具體應用需求,介紹了利用嵌入式CPU Leon3軟核處理器對Virtex系列FPGA的配置進行控制的方法。此系統能夠實現FPGA配置數據的重構,并且減少了外圍CPU和CPLD器件的使用,具有很好的應用價值。

基于LEON3處理器和Speed協處理器的復雜SoC設計實現

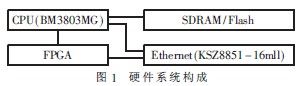

本文就是介紹一款松耦合式可編程專用復雜SoC設計實現,選用LEON3處理器作為MCU,Speed處理器作為Coprocessor。

為了使Leon2得到國內業界的了解和進一步的應用,本文將從Leon2的結構、技術特點、軟硬件的開發過程和應用實例等四個方面進行介紹。在技術特點中,主要介紹了它所遵循的SPARCV8規范、采用的AMBH2.0內部系統總線協議、容錯設計方法和VHDL編程風格等。

為了使LEON2軟核能更快更好地應用于數字機頂盒,選擇先在FPGA開發板上建立基于LEON2處理器的一個原型,通過這個原型對硬件性能進行仿真,并且還可以在線修改程序,這樣就很容易驗證系統的性能,加速軟件開發調試流程。

本文通過將片上系統映射到FPGA,這樣可以在接近運行速度的前提下,驗證硬件和軟件。這樣不僅為軟件部分能盡早地進行開發與調試工作提供了原型,同時也可以在實際運行中發現一些在系統設計中沒有注意的地方。最終可以縮短設計周期,同時為ASIC設計一次成功提供了更大的把握。

評論