基于AD9959的多體制雷達信號源的設計

1引言

本文引用地址:http://www.j9360.com/article/273574.htm隨著雷達技術的發展,出現了多種體制的雷達,比如脈沖多普勒雷達、SAR、相控陣雷達先進,雖然這些雷達的功能不同,但是為了提作用距離和距離向上的分辨率,都彩了大時寬積信號。在雷達信號源設計領域,DDS技術和器件已經得到了很大的發展,相應的出現了很多性能優異的DDS器件,本文旨在介紹一種基于ADI公司的AD9959設計的新型多體制的雷達信號源設計方法,該器件具有穩定度高,相位、頻率和幅度調整靈活,能夠同時產生4路相關信號,信號形式可以任意設定的特點,這些優異的性能在雷達信號源的研制方面都表現出了良好的應用前景。

2 系統硬件設計

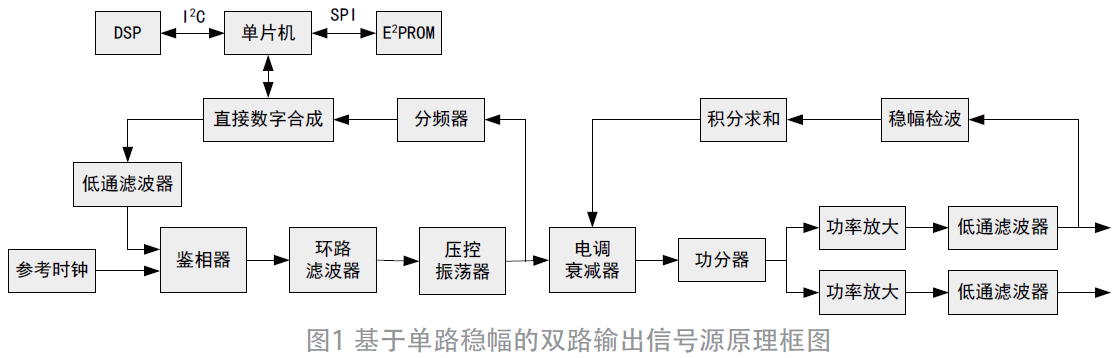

本文設計的多體制雷達信號源是以ADI公司的AD9959為核心,結合FPGA控制電路、信號放大電路構成的。信號參數由主控計算機通過串口進行發送,并同FPGA進行接收,從而控制AD9959完成相應的信號輸出。由于在雷達的實際發射過程中,大部分采用的是大時寬帶寬的脈沖信號,因此在系統硬件設計的架構中,FPGA還完成了一定的脈沖輸出功能,對AD9959輸出的連續波信號進行脈沖調制,從而達到輸出雷達脈沖信號的能力,而輸出的中頻信號經過混頻電路就可以達到雷達發射所需要的頻段。

2.1 AD9959芯片簡介

AD9959是一款性能優異的DDS芯片,主要體現在以下幾個方面:

4路同步輸出通道;

各個通道有獨立的頻率/相位/幅度控制功能;

超強的通道之間隔離度(>65 dB);

線性頻率/相位/幅度掃描能力;

能夠達到16級的頻率/相位/幅度調制能力;

可通過硬件/軟件控制節電模式。

AD9959通過串行I/O提供了多種配置功能,基于這種串行I/O提供的一種SPI模式,同以往的ADI的DDS器件是兼容的。同時,器件采用先進的設計技術,使器件不僅具有優異的性能,而且又具有低功耗的特點。器件集成了具有突出的寬帶和窄帶SFDR特性的4路高速10位DACs。每一個通道,都具有32位頻率控制字,14位相位控制字,10位輸出幅度控制字。REF CLK最高可以達到500 M/s,PLL倍頻器可以通過軟件編程在4~20之間設定。正因為AD9959具有能夠輸出多通道相關信號的能力,所以AD9959可以廣泛地應用于各種場合。

2.2 系統構成

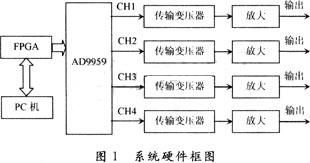

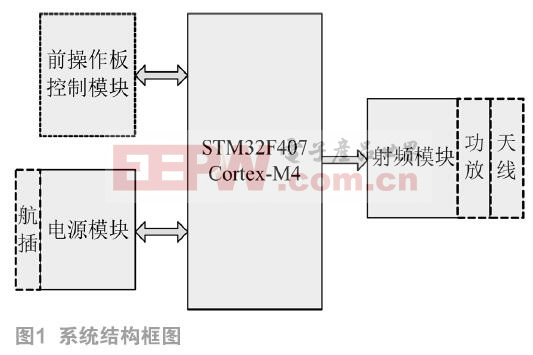

用戶通過計算機將所產生信號的參數傳送給FPGA,FPGA接收到相應的參數后,控制AD9959輸出相應的雷達信號,由于AD9959輸出信號是差分電流信號,因此在系統設計時,采用1:1傳輸變壓器將差分的電流信號轉化為單端的電壓信號,同時為了提高系統的輸出驅動能力,在變壓器后面進行了信號放大,系統框圖如圖1所示。

2.3 系統通信接口及協議

系統主要是由FPGA向AD9959發送命令,從而輸出相應的信號,對于AD9959的控制主要是通過串行總線SCLK和SDIO來實現的,其中 SCLK的最大時鐘速度可以達到200 MHz,AD9959可以通過SDIO的4根數據線(SDIO 0~SDIO 3)同時進行數據傳輸,從而可以使數據吞吐量變為800 Mb/s,以前ADI公司的DDS產品有并行和串行兩種控制模式,比如AD9850,而AD9959這種SPI控制模式,無疑是更加簡潔,對于用戶控制而言也更加方便。AD9959有4種串行控制傳輸模式,分別是Single-Bit Serial(2 and 3-wire)Modes,2-Bit Serial Mode,4-Bit SerialMode。AD9959四個輸出通道共享寄存器0x03~0x18,這種寄存器地址共享模式,能夠使4個通道同時寫入控制字。例如要使 AD9959的4個通道都輸出某個頻率,只需要通過串行總線向AD9959寫入一次即可。如果使4個通道互相獨立操作,可以通過通道選擇寄存器(CSR) 進行選擇。

AD9959的串行工作模式都工作于寄存器級傳輸,而不是字節級傳輸。但是AD9959提供的SYNC I/O功能可以中斷I/O操作,這種模式可以使寄存器的某個字節進行設置,從而減少了設置時間。所有指令都是在SCLK的上升沿寫入,而在SCLK的下降沿讀出的。在本文所設計的雷達信號源中,對于AD9959的控制模式采用了Single--Bit Serial 2-wire Mode,在這種工作模式下,AD9959使用SDIO 0作為數據傳輸管腳,要使AD9959工作于這種模式,可以將CSR寄存器中的CSR<2:1>設置為00即可。在Single-Bit Serial 2-wire Mode傳輸模式下,支持MSB優先和LSB優先兩種模式。

系統通過FPGA對AD9959進行操作,主要分為兩個階段,第一個階段為指令周期,在這個階段把指令寫入到AD9959中,在SCLK的每個上升沿寫入一個比特,并且這個指令字節規定了將要進行的傳輸到底是讀操作還是寫操作,同時包含了寄存器地址;第二個階段為數據傳送周期,主要傳送波形參數的控制字。

圖中完成的時序邏輯控制主要由FPGA來實現,具體的信號參數是通過上位機通過串口發送給FPGA,因此FPGA還完成了串口收發功能,通過串口,系統主控制器(FPGA)不僅可以完成對上位機命令參數的接收,將信號各項參數寫入到AD9959中,同時還可以將AD9959內部狀態信息讀出并且通過串口上傳到計算機。

3 系統軟件設計

3.1 FPGA程序設計

在本文所設計的雷達信號源中,采用了XINUNXSpartan-3系列FPGA,型號為XC23S1000,他具有106個邏輯門,Distributed RAM共120 kb,Block RAM共432 kb,還具有4個DCM單元,最大可用I/O391個。由于系統采用FPGA作為核心控制器件,因此具有很好的擴展性,當對系統的參數發生改變時,只需要對FPGA內部程序加以修改即可。而不用進行硬件的改動,正因為FP-GA具有這樣的優勢,因此使本系統具有很好的靈活性。

通過對FPGA編程,主要完成了對AD9959控制功能和串口收發功能。AD9959內部集成了4個DDS內核,每個DDS內核都集成了32-b的相位累加器和相位一幅度轉換器。每路DDS輸出的信號頻率可以通過下式來計算:

其中,fs表示系統采樣時鐘,FTW表示頻率控制字,fo表示DDS輸出信號頻率。由于在雷達信號源中,線性調頻信號是常用的信號形式,因此這里主要以線形調頻信號作參考。FPGA可以向AD9959發送控制字,從而可以控制輸出信號的起始頻率、調頻斜率系數、截止頻率等。FPGA控制AD9959 寫入指令的時序邏輯圖如圖2所示。

FPGA在系統中不僅完成了控制AD9959的功能,同時還完成符合RS232協議的串口數據的傳送功能,UART功能都采用Verilog HDL語言描述,這樣使系統更加緊湊、小巧。

3.2 PC機程序設計

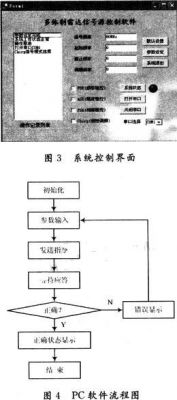

PC機軟件主要完成用戶參數的輸入并且將數據通過RS232串口發送到FPGA,程序采用C編寫,界面上可以輸入生成雷達信號的各種參數,比如信號頻率、起始頻率、截止頻率、調頻斜率,由于AD9959可以生成FSK,PSK,ASK多種體制信號,用戶還可通過下拉列表選擇信號樣式。系統控制軟件界百如圖3所示。

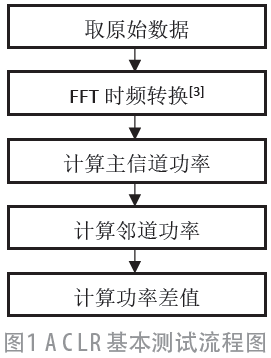

軟件中利Visual Studio.NET中提供的串行通信控件Activex來實現串行數據通信功能,軟件的程序流程如圖4所示。

4 結 語

系統采用FPGA作為核心控制器,不僅完成了對AD9959的控制功能,同時還完成了串行數據傳輸功能,使電路設計更加簡潔并具有很好的擴展性,在系統升級過程中,不必改動硬件設計,只需要將FPGA內部程序進行修改即可完成新的功能。

本文所設計的雷達信號源已經在實際工作中得到很好的應用,系統可以同時輸出4路相參的信號,頻率范圍為10~150 MHz,每路輸出可以單獨控制也可以整體控制,用戶可以通過PC機對系統輸出的信號參數、樣式進行沒定,從而可以很方便地輸出相應的雷達信號。系統具有很強的實用性、靈活性和可擴展性,在實際工作中取得了很好的效果,具有良好的應用前景。

模擬信號相關文章:什么是模擬信號

脈沖點火器相關文章:脈沖點火器原理

評論