多模多制式調制信號發生技術

摘要:隨著通信行業以及數字技術的不斷發展,市場上經常需要多模通信信號或多制式數字調制信號發生器,本文介紹了采用軟件無線電思想,基于“DDR2+FPGA+DAC+DDS+寬帶調制器”的硬件結構的信號發生裝置,實現了TD-SCDMA、WCDMA、TD-LTE、FDD-LTE等多模信號以及BPSK、QPSK、OQPSK、DQPSK、8PSK、16QAM、32QAM、64QAM、2FSK、4FSK、GMSK等數字調制信號的發生,能很好滿足現代信號模擬的實際需求。

本文引用地址:http://www.j9360.com/article/271645.htm1 引言

本設計針對市場的實際需求以及多模通信信號和多制式數字調制信號的特點,設計了以FPGA為主,“DDR2+FPGA+DAC+DDS+寬帶調制器”為硬件架構的多模多制式通信矢量信號發生裝置,利用FPGA可編程的特點,在盡量簡化硬件設計的情況下,可以發射TD-SCDMA、WCDMA、TD-LTE、FDD-LTE等多模信號,發射BPSK、QPSK、OQPSK、DQPSK、8PSK、16QAM、32QAM、64QAM、2FSK、4FSK、GMSK等多調制格式數字調制信號,并可以將用戶數據灌入DDR2,根據用戶實際需要發出,實現復雜信號模擬的功能。

2 設計目的

(1)多模通信信號:GSM/TD-SCDMA/WCDMA/TD-LTE/FDD-LTE等通信制式非信令信號。

(2)多制式調制信號:

● 調制格式:BPSK、QPSK、OQPSK、DQPSK、8PSK、16QAM、32QAM、64QAM、2FSK、4FSK、GMSK;

● 碼元速率:2ksps~40Msps;

● 濾波類型RC、RRC、GAUSS;

● α因子/bt:0.2~1。

(3)用戶數據發射。

(4)將上述信號調制到相應的載波上。

3 硬件設計實現

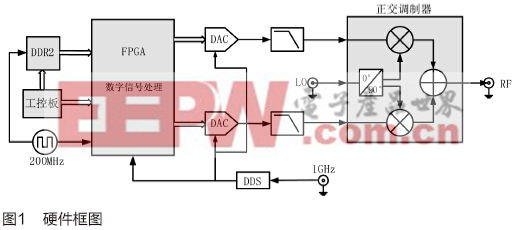

隨著FPGA器件的快速發展,其高速大容量可編程的特點使其得到廣泛應用,對多模多制式的設計需求需要選用FPGA進行設計,它主要完成數字信號處理工作。另外,由于TD-LTE、FDD-LTE的高數據量高速的要求,需要DDR2作為多模信號或用戶數據的存儲介質。在基帶信號發生后,還需要將其DAC轉換后用寬帶正交調制器調制到各自載波上發射。另外,多模多制式信號的發生需要不同碼元速率的設計,需要選用DDS分頻出高分辨率可變時鐘。所以該設計選用“DDR2+FPGA+DAC+DDS+寬帶調制器”硬件架構,其框圖如圖1。

4 FPGA設計實現

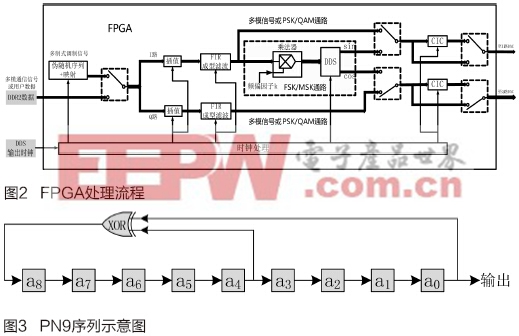

該設計的重點是對多模多制式調制信號進行數字信號處理,由FPGA完成,包括多模信號或用戶數據的插值、FIR成型濾波、CIC插值等處理;以及多制式信號的偽隨機信號產生、映射、插值、FIR成型濾波、頻偏系數生成、DDS及CIC插值等處理。FPGA處理流程見圖2。

模擬信號相關文章:什么是模擬信號

濾波器相關文章:濾波器原理

fpga相關文章:fpga是什么

濾波器相關文章:濾波器原理

通信相關文章:通信原理

低通濾波器相關文章:低通濾波器原理

電源濾波器相關文章:電源濾波器原理

負離子發生器相關文章:負離子發生器原理 矢量控制相關文章:矢量控制原理 數字濾波器相關文章:數字濾波器原理 離子色譜儀相關文章:離子色譜儀原理

評論