詳解“工藝制程”:為何20nm芯片更強大

本文引用地址:http://www.j9360.com/article/266107.htm

?

當推出新款處理器的時候,制造商們總喜歡講述“更小的納米制程工藝”、“更強大的性能”、以及“更優異的能效表現”等概念。不過,很多人或許難以理解,為何在做得更小、功耗更低的同時,其性能反而還可以更加強大呢?有鑒于此,外媒PhoneArena特地撰寫了一篇文章,為我們解釋與“制程”相關的的一些問題。

?

首先,什么是納米?

從本質上來說,一顆微處理器就是由采用不同材料制成的許多“層”堆疊起來的電路,里面包含了晶體管、電阻器、以及電容器等微小元件。

不過它們與被你扔進垃圾堆的大塊頭所采用的常規元器件很是不同,因為它們的尺寸已經小得肉眼難以看清,而規模更是可以讓你感到震驚。

在這些由元器件組成的“大軍方陣”中,組件間的距離通常用毫微米進行衡量。如果覺得“十億分之一米”的概念不好記,那你也可以用“納米”(nanometers)來描述它。

最后,間距越小,可以排布在芯片上的元器件就可以更多。

其次,為什么制程更小更節能?

答案是:縮減元器件之間的距離之后,晶體管之間的電容也會更低,從而提升它們的開關頻率。

由于晶體管在切換電子信號時的動態功率消耗與電容成正比,因此它們才可以在速度更快的同時,達到更加省電。

另外,這些更小的晶體管只需要更低的導通電壓,而動態功耗又與電壓的平方成反比(能效又提升)。

最后,推動半導體制造商向更小的工藝尺寸進發的最大動力,就是成本的降低。組件越小,同一片晶圓可切割出來的芯片就可以更多。

即使更小的工藝需要更昂貴的設備,其投資成本也可以被更多的晶片所抵消。

?

最后一點,為何制程工藝的飛躍幾乎都是每2年一次?

有利也有弊,在制程更小更省電的同時,晶體管的電流也更易泄露——即使其處于“關閉”狀態。如此一來,又會導致芯片“更費電”。

在理想世界中,這些元器件方陣會是完全穩定的。而隨著電子設備變得越來越小,波動、漸變和擴散都會對其造成很大的影響。

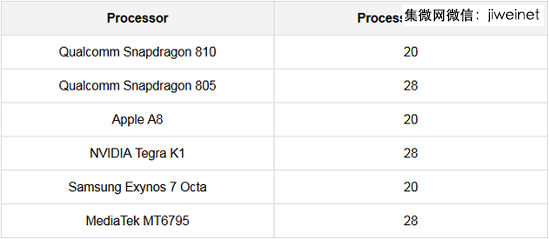

那么,如何在“制程”與“穩定”之間達成平衡呢?上方的表格就列明了當前市面上可以達到的移動芯片的“極限”。

當然,制造商們對于“極限”的追求是永無止境的。或許在不遠的將來,我們就能迎來量產版的“單原子大小”工藝制程的芯片了。

評論