FPGA研發之道(9)架構設計漫談(四)并行與復用

FPGA其在眾多器件中能夠被工程師青睞的一個很重要的原因就是其強悍的處理能力。那如何能夠做到高速的數據處理,數據的并行處理則是其中一個很重要的方式。

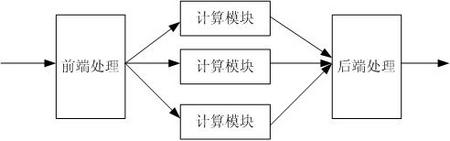

本文引用地址:http://www.j9360.com/article/264454.htm數據的并行處理,從結構上非常簡單,但是設計上卻是相當復雜,對于現有的FPGA來說,雖然各種FPGA的容量都在增加,但是在有限的邏輯中達到更高的處理能力則是FPGA工程師面臨的挑戰。常用并行計算結構如下圖所示:

?

上圖中:前端處理單元負責將進入數據信息,分配到多個計算單元中,圖中為3個計算單元(幾個根據所需的性能計算得出)。然后計算單元計算完畢后,交付后端處理單元整合為統一數據流傳入下一級。如果單個計算單元的處理能力為N ,則通過并行的方式,根據并行度M,其計算能力為N*M;在此結構中,涉及到幾個問題:

一, 前端處理單元如何將數據分配到多個計算單元,其中一種算法為round-robin,輪流寫入下一級計算單元,這種方式一般使用用計算單元計算數據塊的時間等同。更常用的一種方式,可以根據計算單元的標示,即忙閑狀態,如果哪個計算單元標示為閑狀態,則分配其數據塊。

二, 計算單元和前后端處理之間如何進行數據交互。一般來說,計算單元處理頻率較低,為關鍵路徑所在。前后端處理流量較大,時鐘頻率較高,因此通過異步FIFO連接,或者雙端口RAM都是合適的方式。如果數據可分塊計算,且塊的大小不定,建議使用FIFO作為隔離手段,同時使用可編程滿信號,作為前端處理識別計算模塊的忙閑標示。

三, 如果數據有先后的標示,即先計算的數據需要先被送出,則后端處理模塊需要額外的信號,確定讀取各個計算模塊的順序。這是因為:如果數據等長,則計算時間等長,則先計算的數據會先被送出。但是如果數據塊不等長,后送入的小的數據塊肯能先被計算完畢,后端處理單元如果不識別先后計算的數據塊,就會造成數據的亂序。這可以通過前端計算單元通過小的FIFO通知后端計算單元獲知首先讀取那個計算單元輸出的數據,即使其他計算單元輸出已準備好,也要等待按照順序來讀取。

數據的并行處理是FPGA常用的提升處理性能的方法,其優點是結構簡單,通過計算單元模塊的復用達到高性能的處理。缺點,顯而易見就是達到M倍的性能就要要耗費M倍邏輯。

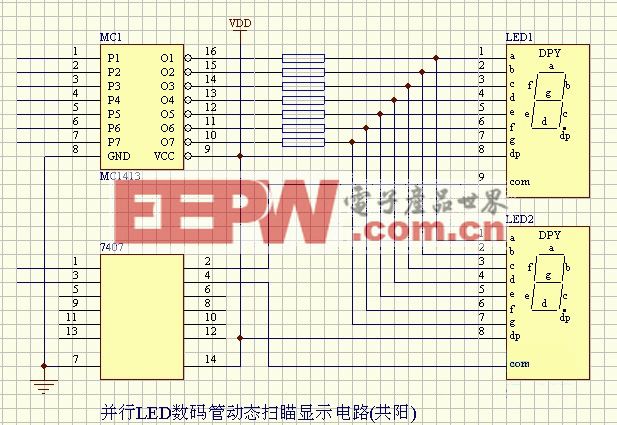

與之相反減少邏輯的另一種方式,則是復用,即一個處理能力較強的模塊,可以被N的單元復用,通過復用,而不用每個單元例化模塊,可以達到減少邏輯的效果,但控制復雜度就會上升。其結構圖如下所示:

?

上圖復用的結構圖中,分別介紹了流過模式復用和調用模式復用。流過模式下,計算單元處理多路數據塊,然后將數據塊分配到多路上,這種情況下,通過round-robin可以保證各個通路公平機會獲得計算單元。其處理思路與上圖描述并行處理類似。

調用模式下,計算單元被多個主設備復用,這種架構可以通過總線及仲裁的方式來使各個主設備能夠獲取計算單元的處理(有很多成熟的例子可供使用,如AHB等)。如果多個主設備和多個計算單元的情況,則可以不通過總線而通過交換矩陣,來減少總線處理帶來的總線瓶頸。

實際應用場合,設計的架構都應簡單實用為好,交互矩陣雖然實用靈活,但其邏輯量,邊界測試驗證的難度都較大,在需要靈活支持多端口互聯互通的情況下使用,可謂物盡其用。但如果僅僅用于一般計算單元能力復用的場景,就屬于過度設計,其可以通過化簡成上述兩種簡單模式,達到高速的數據處理的效果。

并行和復用,雖然是看其來屬性相反的操作,但其本質上就是通過處理能力和邏輯數量的平衡,從而以最優的策略滿足項目的需要。設計如此,人生亦然。

fpga相關文章:fpga是什么

評論