什么是FSL總線

FSL(Fast Simplex Link,快速單向鏈路)總線,是Xilinx公司為其FPGA器件開發的,可以實現用戶IP核與軟核處理器的高速連接。

本文引用地址:http://www.j9360.com/article/258965.htmFSL總線

FSL總線接口

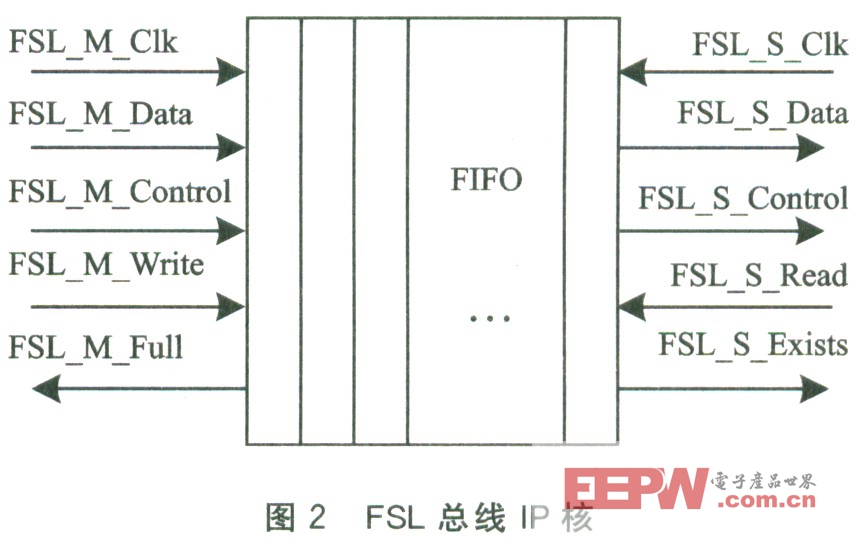

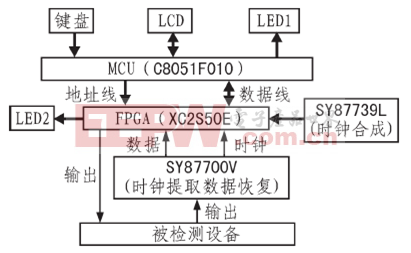

FSL總線是一個基于FIFO的單向點對點通信總線,主要用于FPGA的兩個模塊問進行快速的通信。FSL總線IP核結構如圖2所示,FSL接口的I/O信號如表2所列。

該接口的主要特點:

◆單向的點對點通信;

◆非共享的無仲裁通信機制;

◆支持控制位與數據分離的通信;

◆基于FIFO的通信模式;

◆可配置的數據寬度;

◆高速的通信性能(獨立運行達到600 MHz)。

FSL總線的寫操作時序

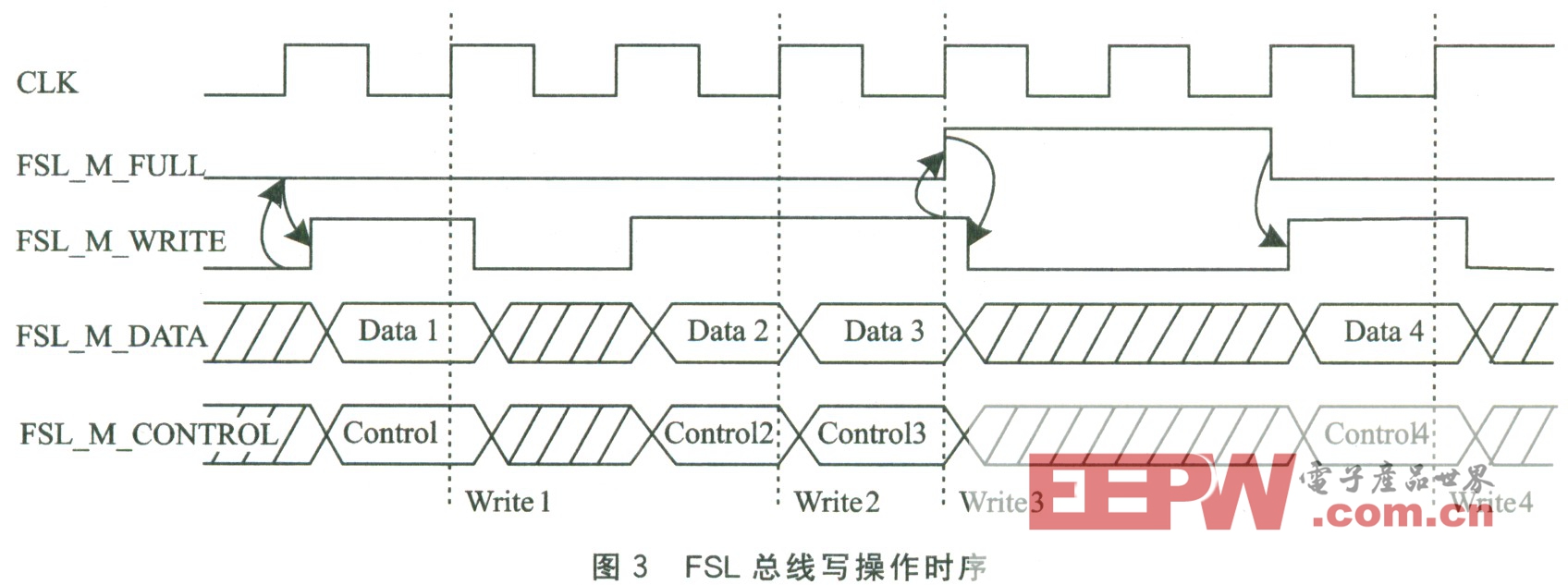

對FSL總線的寫操作是由FSL_M_Write信號控制的。圖3是FSL總線的寫操作時序。FSL主設備在第一個時鐘上升沿檢查到FSL_M_Full 信號未置高,就允許主設備將FSL_M_Write置高,并將FSL_M_Data和FSL_M_Control推上總線,在下一個時鐘周期這些數據就被總線讀取并送入FIFO了。圖中的Write2和Write3是一組“背靠背”的連續寫操作。在Write3時,FIFO滿使得FSL_M_Full信號被置高,迫使主設備取消自己的FSL_M_Write信號,直到一次讀操作將FSL_M_Full置低后,才可以發起另一次寫操作。因此,圖中暗示著在 Write4處也發生了一次從設備的讀操作,否則FSL_M_Full將再次置高。

FSL總線讀操作時序

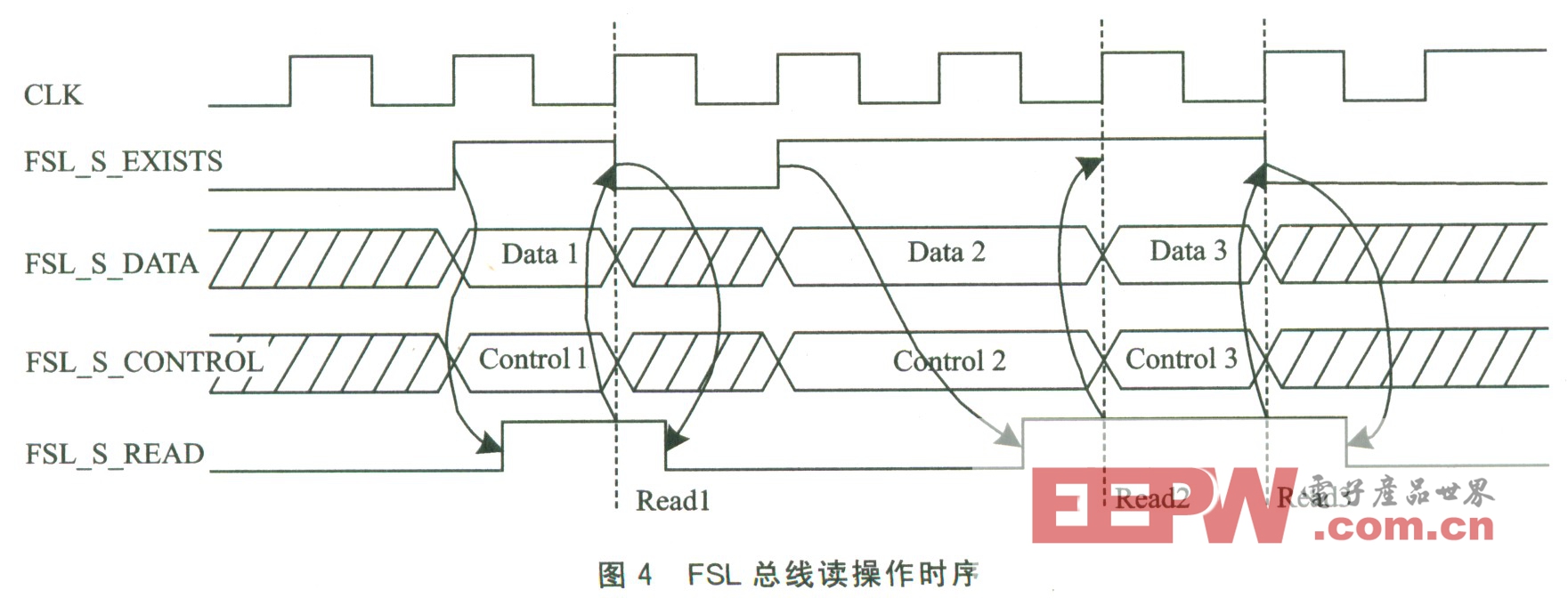

對FSL總線的讀操作是由FSL_S_Read信號控制的,圖4是FSL從設備的3次讀操作時序。當FSL總線上存在有效數據(FSL_S_Exists =‘1’),FSL_M_Data上的數據和FSL_M_Control上的控制位就立即可以被FSL從設備讀取。一旦從設備完成讀操作, FSL_S_Read信號必須置高一個時鐘周期,以確認從設備成功完成了一次讀操作。在讀操作發生后的時鐘上升沿(圖中Read2處), FSL_M_Data和FSL_M_Control會被更新為新數據,同時FSL_S_Exists和FSL_M_Full信號也會被更新。同樣,這里暗示著在Readl和Read2之間發生了兩次主設備的寫操作。

FSL總線用法

使用FSL總線IP核的設備間通信

目前Xilinx提供的FSL總線IP核的版本是FSL_V20。兩個設備要使用FSL進行數據傳輸,就必須分別作為主設備或從設備連接到FSL核上。如果需要進行雙向的傳輸,只要兩個設備分別作為主從設備,使用兩個FSL核連接即可。

無論是作為主設備或是從設備,都需要通過在設備的微處理器外設描述文件(MPD)中進行相應的定義,以實現所需類型的FSL接口。下面這段代碼就是一個分別定義了FSL主設備接口FSL_OUT和從設備接口FSL_IN的MPD文件:

BEGIN my_fsl_peripheral

OPTl0N IPTYPE=PERIPHERAL

OPTl0N IMP_NETLIST=TRUE

BUS_INTERFACE BUS=FSL_IN,BUS_STD=FSL,BUS TYPE=SLAVE

BUS_INTERFACE BUS=FSL_OUT,BUS_STD=FSL,BUS_TYPE=MASTER

##Ports

PORT CLK=””,DIR=IN,SIGIS=CLK

PORT RESET=””。DIR=IN

PORT FSL_S_READ=FSL_S_Read,DIR=out,BUS=FSL_IN

PORT FSL_S_DATA=FSL_S_Data,DIR=in,VEC=[o:31],BUS=FSL_IN

PORT FSL_S_CONTROL=FSL_S_Control,DIR=in, BUS=FSL_IN

PORT FSL_s_EXISTS=FSL_S_Exists,DIR=in,BUS=FSL_IN

PORT FSL_M_WRITE=FSL_M_Write,DIR=out,BUS=FSL_OUT

PORT FSL_M_DATA=FSL_M_Data,DIR=out,VEC=[o:31],BUS=FSL_OUT

PORT FSL_M_CONTROL=FSL_M_Control,DIR=out, BUS=FSL_OUT

PORT FSL_M_FULL=FSL_M_Full,DIR=in,BUS=FSL_OUT

通過FSL與MicroBlaze通信

MicroBlaze軟核的FSL總線接口支持最多8對FSL連接,具體實現多少接口由系統硬件描述文件(MHS)中的參數C_FSL_LINKS決定。默認情況下該參數為0,表示不實現FSL接口。當需要使用FSL總線把MicroBlaze和FPGA中的一個或多個邏輯模塊連接起來時,必須設置該參數的值為相應的模塊數。該參數的取值范圍是0~8。

在MicroBlaze指令集中還有針對FSL總線操作的指令,它們分別是:

◆get,put——阻塞式數據讀寫FSL,控制信號被置為0;

◆nget,nput——非阻塞式數據讀寫FSL,控制信號被置為0;

◆cget,cput——阻塞式控制位讀寫FSL,控制信號被置為1;

◆ncget,ncput——非阻塞式控制位讀寫FSL,控制信號被置為1。

FSL總線應用實例

在下面的實例中,嘗試通過FSL總線技術,將實現特定函數功能的用戶自定義IP核整合到MicroBlaze軟核系統中,以實現硬件加速的目的。這里以一個矢量漢字(vector font)還原功能的硬件模塊的整合為例,說明FSL總線的應用過程。所使用的開發平臺是Memec Insight公司生產的Virtex—II系列的MicroBlaze開發板,板上采用的FPGA器件為Virtex—II 1000,系統時鐘為100 MHz,開發工具為Xilinx公司的EDK 6.3及ISE 6.3。

FSL總線應用方案

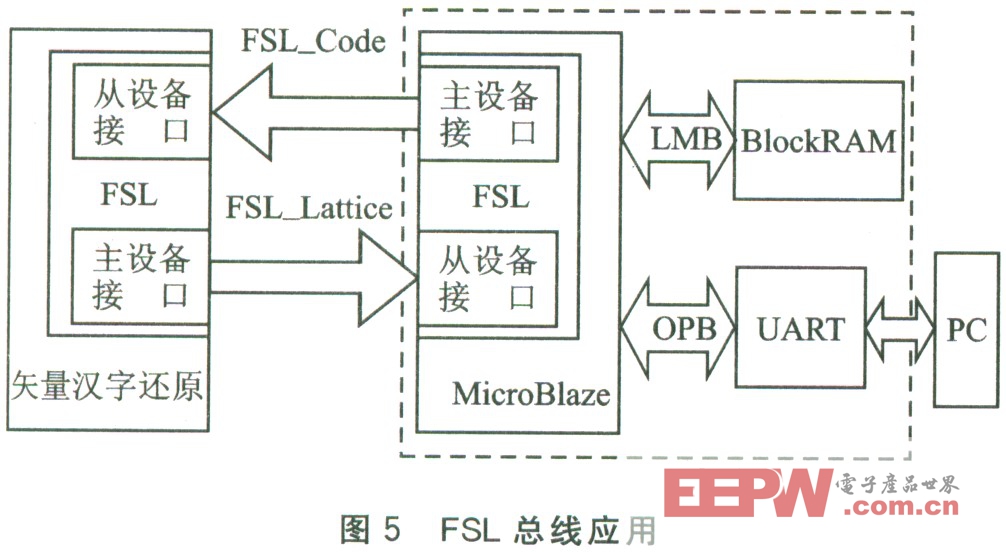

如圖5所示,vectOr_font核通過FSL_Code-與FSL_Lattice兩條FSL總線與MicroBlaze軟核直接相連。

對于FSL_Code總線,MicroBlaze核是主設備,而vector_font核是從設備。這樣MicroBlaze可以通過 FSL_Code總線向vectOr_font核發送漢字的區位碼(或者其他格式的漢字編碼,由使用的矢量字庫和還原算法決定)以及漢字的屬性信息(如字體、大小等)。

對于FSL_Lattice總線則正好相反。vector font 核作為主設備可以通過它向MicroBlaze核發送經過還原處理后的漢字點陣數據以及漢字點陣尺寸信息(用于將點陣數據在顯存中組織成正確的顯示格式)。

數據傳輸指令與控制位指令的應用

FSL 提供的獨立于數據傳輸的控制位可以用來對正在傳輸中的數據進行標記。為了區分區位碼數據與漢字屬性數據,以及點陣數據與漢字點陣尺寸數據。 MicroBlaze分別通過FSL的數據傳輸指令和控制位傳輸指令來發送漢字的區位碼和漢字屬性信息,接收點陣數據和漢字點陣尺寸信息。對應的實現代碼如下:

//使用非阻塞的數據寫函數向FSL總線寫入漢字區位碼Microblaze_nbwrite_datatsl(code,O)

//使用非阻塞的控制位寫函數向FSL總線寫入漢字屬性信息maicroblaze_cnbwrite_cnlfsl(attibute,O)

//使用非阻塞的數據讀函數從FSL總線讀取漢字點陣數據microblaze_nbread_datafsl(1attice[i],O)

//使用非阻塞的控制位讀函數從FSL總線讀取漢字點陣尺寸信息microblaze_cnbread_cnlfsl(size,O)

代碼中用到的與FSL有關函數的定義,都在include目錄下的mb_interface.h文件中。其中,各函數的第二個參數代表進行讀寫操作的 FSL總線接口的編號,對應Mi—croBlaze軟核的8對FSL接口。該參數的取值范圍從0到7。本例中,MicroBlaze只使用了一對FSL接口,故而值為0。

實現步驟

首先,在Base System Wizard中設計圖5虛線框中所示的一個簡單的MicroBlaze嵌入式處理器系統。然后,在XPS集成開發環境下完成用戶自定義IP核(本例中即 vectoz__font核)的添加、Microblaze核FSL接口的添加(設置參數C_FSL_LINKS=1),同時添加兩個FSL總線IP核,分別用于實現FSL_Code和FSL_Lattice總線。另外,將兩個FSL總線IP核的參數C_USE_CONTROL置為1,以打開FSL總線的控制位傳輸功能。所有這些改動,最后都會被更新到MES文件中。這樣,硬件平臺生成工具platgen就可以根據它生成所需要的FPGA配置文件了。

硬件的實現完成后,進行相應軟件參數的設置,如將系統標準輸入輸出設備指向UART模塊等。然后,用庫生成工具libgen,根據MSS(系統軟件描述文件)文件,將所需外設函數庫的頭文件添加進工程中。

通過調用這些函數,可以操作和控制這些外設。通過Tool項里的build命令,調用mb—gcc:編譯工具,將編寫的應用程序編譯成ELF文件,再用 updatebitstrcam命令將程序代碼對應的RAM初始化數據添加到前面生成的FPGA配置文件中,生成最終的bit配置文件。最后,使用 download命令將bit文件下載到目標板中。

以上就是整個FSL應用實例設計的實現過程。本例只是為了說明FSL總線的使用。實際應用中,還可以根據具體情況通過FSL,將更多的用戶自定義IP核(如DCT、FFT等)添加到.MicroBlaze軟核系統中去。

結 語

在嵌入式系統的開發中,人們一直希望能夠有一個滿足自己需要的“定制”的嵌入式處理器,而不是手頭大量存在的通用微處理器。但是,直接將用戶自定義IP核添加到處理器核中,不僅受到處理器原架構的束縛,還有可能降低處理器的性能(處理器工作頻率);而通過與內部寄存器直接相連的FSL接口,用戶自定義IP 可以在不破壞處理器原有結構的情況下,緊密地與MicroB- laze軟核結合在一起。這樣,即使關鍵路徑覆蓋了用戶IP 核,由于它在處理器內核之外,也不會導致處理器時鐘頻率的降低。

通過對FSL總線的分析以及上述實例的驗證,證明了在基于MicroBlaze的SoC 系統設計中,一方面可以針對具體應用進行“量體裁衣”式的設計;另一方面,利用其專用的FSL總線接口技術,實現嵌入式軟處理器系統與用戶自定義邏輯的整合,從而在不提高系統主頻的前提下,通過部分函數功能的硬件實現來提升系統的性能。

評論