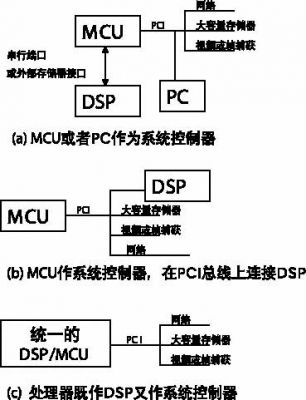

新一代PCI背板電源管理需求

高速匯流排提高電源設計難度

隨著許多高速處理器、大容量硬碟和磁碟陣列、顯示卡、乙太網路和光纖資料通信、以及存儲器陣列等設備的通信速度不斷加快,使用更快速的匯流排介面來符合其應用需求成為必要。

現代半導體技術能制造出比以前更快的邏輯電路,但僅靠提高邏輯電路速度并不足以加快匯流排速度。匯流排架構工程師必須處理匯流排電容、因為信號線長度不同所造成的信號歪斜現象、難以預測的匯流排負載變化、以及系統零組件的誤差。匯流排速度越快,電壓就必須越精確。而這些問題都與俗稱為I/O電源或VIO.的匯流排收發器電源供應習習相關,因此現代匯流排必須小心設計其電源才能有效發揮最大效能。

新舊PCI可相容

回溯相容性是PCI匯流排的最大優勢。PCI特別工作小組已發展出一套方法讓PCI擴充槽能同時支援新型與舊規格的PCI電路板。早期的PCI電路板和PCI-X 1.0(又稱為mode-1)電路板都使用3.3V VIO,而PCI-X 2.0 266MHz和533MHz(又稱為mode-2)電路板使用的則是1.5V VIO電壓。誤用3.3V電源的mode-2電路板會發生故障;而誤用1.5V電源的舊規格或mode-1電路板,則可能會沒有足夠的電壓在匯流排產生邏輯 “1” 信號。

原始的PCI標準是以不同的接腳邊緣外形讓5V和3.3V電路板共存,但這種做法無法提供回溯相容性。PCI-X 2.0則是借用現代高效能微處理器技術,也就是透過邏輯電路來選擇電壓(logic-selectable voltage)來解決此問題。

PCI電路板連接座上有個稱為PCIXCAP的PCI-X相容性接腳,PCI系統會利用系統電路板上的模擬數字轉換器測量PCIXCAP的電壓值以決定PCI電路板速度。傳統PCI電路板會將PCIXCAP接地,使擴充槽控制器將匯流排速度限制在33MHz。PCI-X 66MHz電路板會在PCIXCAP接腳加上10kΩ下拉電阻,讓PCI-X以66MHz速度操作;PCI-X 133MHz電路板則會讓PCIXCAP處于浮動狀態,以啟動133MHz操作模式。

這種技術還能根據PCIXCAP共用接腳電壓來設定整個匯流排。比方說,只要有一張PCI電路板將PCIXCAP接地,整個匯流排就會使用33MHz;PCIXCAP接腳若處于浮動高電位,就表示所有PCI電路板皆為PCI-X 133MHz,使匯流排進入133MHz操作模式。若有部份電路板在PCIXCAP加上10kΩ下拉電阻,PCIXCAP接腳電壓就會低于浮動狀態的高電壓,但仍高于接地電壓,此時匯流排會在PCI-X 66MHz速率下操作。

PCI-X 2.0定義兩種新的下拉電阻值:PCI-X 266MHz的3.16kΩ以及PCI-X 533MHz的1.02kΩ,來進一步擴大此技術,使操作速度增加為五種。系統可以根據PCIXCAP模擬數字轉換器所提供的資訊來設定匯流排速度與VIO電壓。

工程師還需解決許多其他問題才能完成64位元266MHz擴充槽實作。橋接技術速度雖然已能讓一個橋接器支援6個32位元的66MHz PCI擴充槽,但目前仍只能處理2個64位元的133MHz PCI-X 1.0匯流排擴充槽;266MHz以上的PCI匯流排更要將橋接器直接連線至擴充槽,才能滿足兩者之間的超高資料速率要求。

PCI VIO規格

使用3.3V或5V I/O電源和較慢的資料速率時,就算電源供應電壓略有變動,PCI系統所輸出的低電位和高電位電壓仍能達到TTL規格要求。但如果VIO降到1.5V,資料速率又增加至266MHz以上,信號振幅范圍將大幅縮小,信號穩定時間則相對變得更重要。

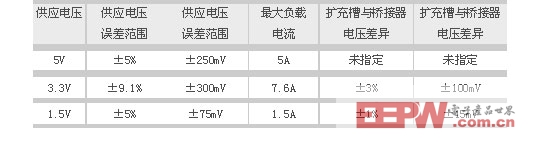

PCI規格對于不同的VIO電壓要求如下:

PCI-X mode 1要求擴充槽和橋接器的3.3V VIO電壓相差不能超過±100mV;這就表示橋接晶片的VIO電壓必須在擴充槽VIO電壓的100mV范圍內,以便忍受電流感測電阻、獨立的電源切換FET開關電晶體、和信號線的可能電壓降。但若VIO電壓為1.5V,擴充槽與橋接器的電壓就不能相差超過±15mV;此時唯有讓它們使用同一組電源,并以又短又粗的導線將其電源接點連接在一起,才能確保擴充槽與橋接器的電壓相差在要求范圍內。

針對VIO電壓的要求也帶來了許多新限制。舉例來說,橋接晶片必須能開啟和關閉VIO電壓,以及選擇電壓值在3.3V與1.5V之間。電源供應選擇開關在提供電源給擴充槽負載(最高1.5A)和橋接晶片負載時(最高1.5A以上,視橋接晶片而定),其電壓降不能超過±75mV。

VIO電源實作

有些系統會用它的1.5V電源層,提供VIO電壓給mode-2橋接器和PCI-X擴充槽。這些系統只要遵守下列簡單規則,就能使用切換電路來提供VIO電壓:

1. 以寬而短的線路將VIO電壓傳送給橋接器和擴充槽;

2. 略為提高1.5V電源層的電壓;

3. 使用導通阻抗極低的功率FET電晶體和電流感測元件;

4. 在「阻隔串接線路」(blocking series connection)上,利用兩顆FET開關電晶體將1.5V電源送到橋接器和擴充槽;如此一來,無論擴充槽電壓為0V或3.3V,只要FET處于截止狀態,就不會有電流從擴充槽通過FET的體二極管進入1.5V電源層。

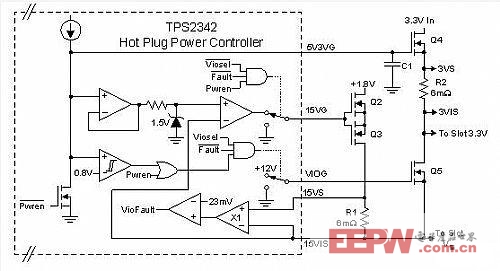

除了采用上述的切換電路之外,也能以1.8V電源供應器來提供VIO電壓給mode-2擴充槽和橋接晶片,然后再利用低壓降線性穩壓器將1.8V降壓至1.5V電壓。這種做法可使用成本較低的FET電晶體,而對于電路板繞線要求也比較寬。比方說,設計人員可以使用UC382-1之類的低壓降穩壓元件,或圖1所示的TPS2342熱插拔電源控制器;此時功率FET將同時扮演電源選擇器、穩壓器、和熱插拔電源開關等多種角色。

圖1:采用TPS2342 PCI-X 2.0熱插拔控制器的1.8V和3.3V VIO電壓選擇電路。它會在匯流排處于mode-2模式時,透過放大器驅動Q2和Q3,使+1.8V電壓降為1.5V。

擴充槽VIO接腳與元件15VIS接腳之間的連線極為重要;由于它同時擔任著電流感測和穩壓感測等功能,所以在繞線時需特別注意。

若系統無法提供低電壓電源,也能利用可程式交換式穩壓器來提供VIO電壓;例如使用可接受+12V輸入電源的PTH05000 VRM穩壓模組提供3.3V或1.5V電壓,或是採用內建FET電晶體的TPS54310 SWIFT等交換式穩壓元件。

評論