數字電源UCD92xx的輸出電壓波形優化與分析

基于UCD92xx與UCD7xxx的非隔離數字電源,其輸出電壓在軟啟動階段經常出現“臺階”現象,波形不平滑,尤其是輸出電壓設定為較低值時,如1.0V。這種“臺階”現象與UCD92xx 軟啟動的設計原理有關,但完全可以通過一定的措施來優化并最終解決。本文從UCD92xx的環路和最小占空比寬度兩個方向進行優化與分析,最終取得了理想的效果。

1、軟啟動原理及待優化輸出電壓波形

數字電源UCD92xx的軟啟動是通過對參考電壓以步進方式增加來實現的,整個過程是由芯片內部的軟件自動完成的。在一款基于UCD9224和UCD74120的單板上測試時發現,其輸出電壓波形在軟啟動階段有明顯的“臺階”現象,波形不平滑。

1.1 數字電源軟啟動原理介紹

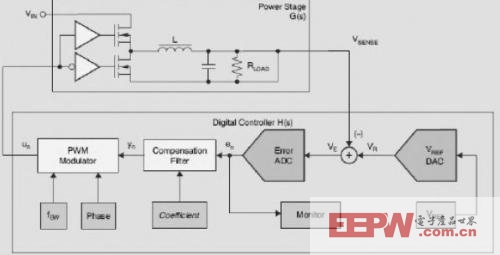

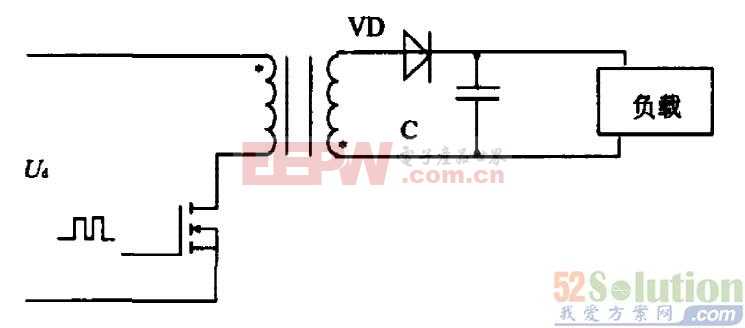

圖1所示的是數字電源UCD92xx的功率支路和控制支路。控制支路主要集成在UCD92xx芯片內部,包含誤差生成及模數轉換,環路補償,PWM計算及產生等。其中,參考電壓(VREF)電壓的設置亦包含在控制支路。

依據軟件算法,在軟啟動階段,VREF每100μs增加一次,直至軟啟動完成,即輸出電壓達到最終的設定值。例如,輸出電壓設定為1.0V,軟啟動的時間設置為4ms,則在軟啟動階段輸出電壓每一次增加25mv,直至達到1.0V。

圖1:數字電源功率級和控制級框圖

1.2 待優化的輸出電壓波形

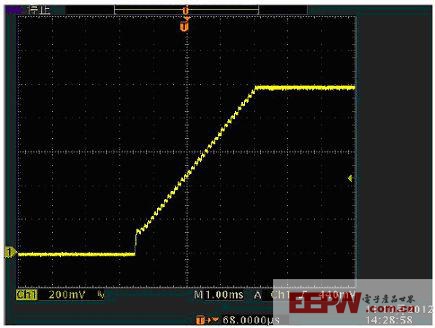

圖2所示的是輸出電壓波形,可以觀察到在軟啟動階段輸出電壓的波形不夠平滑,有明顯的“臺階”現象。

該波形是在一款基于UCD9224和UCD74120的參考版上測得。主要測試條件為:測試環境常溫,輸入電壓為12V,輸出電壓為1.0V,輸出端帶載20A。另外,測試時,數字環路的詳細配置見下文2.4節。

圖2:輸出電壓波形

1.3輸出電壓“臺階”現象的初步分析

圖3所示的是時間軸展開后觀察到的輸出電壓波形。通過測量可知,每經過100μs輸出電壓增加一次,增加的幅度大約為23mV,與理論計算值25mV基本一致。

同時也可以觀察到,輸出電壓的每一次增加都是很快的完成,而不是緩慢增加。從功率級支路上分析,這是由于占空比快速增加造成。從控制級支路分析,則原因可以初步歸結為環路過快造成的。

圖3:輸出電壓的步進幅度

2 數字電源模擬前端及環路

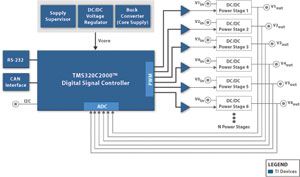

數字電源控制環路包含了模擬前端,數字環路補償等模塊,在配置環路時需要綜合考慮。其中,數字環路還包含非線性增益模塊,使能后可以有效提升整個電源的動態響應性能。

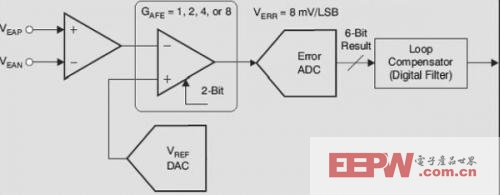

2.1 數字電源模擬前端(AFE)

圖4紅色框內電路為數字電源模擬前端(Analog-Front End,AFE)的一部分,其增益可以設置為1,2,4,8等四個不同的值。設置不同的增益,則ADC的輸出精度也隨之不同,比如設置增益為4,則輸出精度為2mV;設置增益為1,則輸出精度為8mV。

在相同輸入誤差(VEAP-VEAN)的情況下,不同的AFE 增益值將直接影響環路指標。其影響趨勢為,增益越大,環路帶寬越寬。

圖4:數字電源的模擬前端

評論