Giga ADC 介紹及雜散分析(下)

3、Giga ADC雜散的分析

ADC應用中,輸出的雜散信號決定了ADC的動態范圍。在傳統的流水線ADC中,起決定作用的主要是諧波雜散,即輸入信號的二次、三次或更高次諧波混疊進入第一個Nyquist區。除此以外,GigaADC的interleave架構帶來了其它雜散。如前文說提到的,為了達到更高的采樣速率,每路ADC實際包括兩個子ADC,這兩個子ADC工作在interleave模式下。在這種情況下,兩路子ADC之間的失配將會產生新的雜散信號。總體來說,Giga ADC的雜散主要分為三類雜散信號:1)interleave雜散;2)固定頻點雜散;3)和輸入信號相關的雜散。

3.1 Interleave相關的雜散

Interleave模式,如Figure7所示,就是相同的輸入信號,輸入到兩個(或N個)采樣率相同,但采樣時鐘相位相反(或相差2π/N)的ADC中,從而達到采樣率增倍的目的。但由于兩路ADC不可能完全一致,存在一些失配,從而導致了一些輸出雜散的生成。這些失配包括偏置誤差、增益誤差以及采樣時鐘的相位誤差。

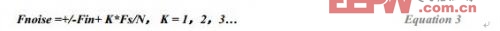

這里假定:N:一路ADC中包含的子ADC個數Fin:輸入有用信號Fnoise:輸出的雜散信號Fs:ADC采樣時鐘

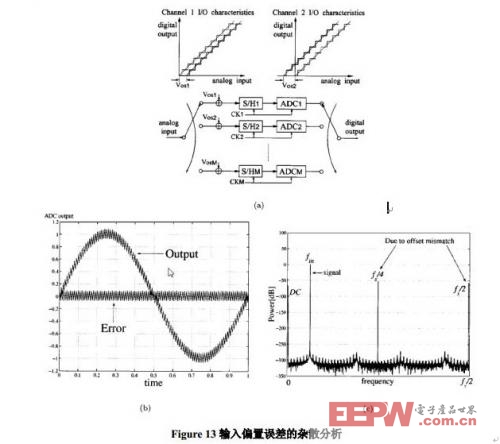

3.1.1輸入偏置誤差

假定ADC其它參數都是理想的,只考慮輸入偏置誤差。通過數學分析可以得到,輸入偏置誤差帶來的雜散主要分布在

從Figure13可以看出,輸入偏置誤差帶來的雜散和輸入信號的幅度和頻率沒有關系,從頻域上看,均勻的分布在第一Nyquist區。由輸入偏置帶來的雜散固定的分布在公式一給出的各個頻點。

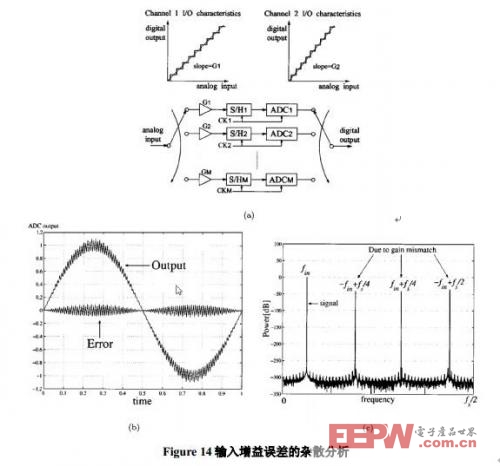

3.1.2輸入增益誤差

假定輸入電路除增益誤差以外,其它參數都是理想的,可以看出當輸入信號幅度增大時,增益誤差也隨之變大。輸出的誤差信號類似于輸入信號的一個調幅輸出,可以得到,增益誤差導致的雜散信號出現位置如下:

從分析可以看出,由于增益誤差導致的輸出雜散幅度和輸入信號的頻率無關,但和輸入信號的幅度有關,輸入信號幅度變大時,雜散幅度增加;反之亦然。

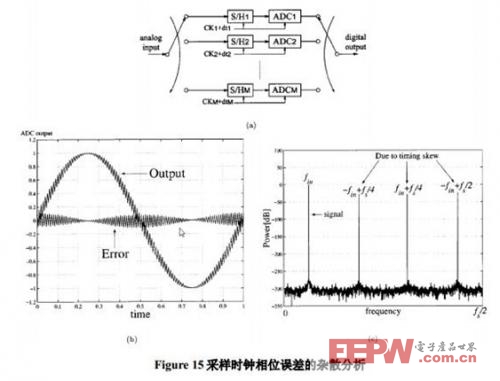

3.1.3采樣時鐘的相位誤差

如果兩個或多個采樣時鐘之間存在相位誤差(skew),同樣會帶來雜散。由于相位誤差帶來的誤差最大出現在輸入信號壓擺率最大的地方,即過零點,即這類雜散類似于輸入信號的調頻輸出。雜散信號出現的位置在:

采樣時鐘的相位誤差和輸入增益誤差帶來的雜散位置相同,但相位誤差輸出的雜散和輸入頻率有關,當輸入頻率越高,誤差越大;而偏置誤差和增益誤差帶來的雜散和輸入頻率無關。

3.2固定頻點雜散

相對于interleave雜散,固定頻點雜散和輸入信號的頻點無關,主要取決與系統時鐘,ADC及子ADC的采樣時鐘,數據輸出的隨路時鐘以及系統中其他時鐘源的耦合干擾。固定頻點雜散因為位置固定,應用中很容易預判這些雜散,從而在系統設計中規避這些雜散存在的頻點。

3.2.1采樣時鐘雜散

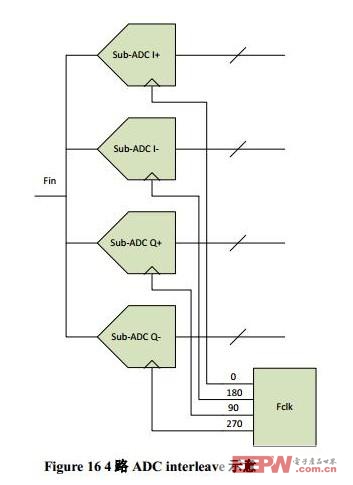

如Figure 16所示,當四個ADC工作在interleave模式下,四個ADC的采樣率都是Fclk,但相位相差90度,這樣整個ADC通道的實際采樣率為4*Fclk;輸出的頻譜中,在Fclk頻點處有一個固定的采樣時鐘雜散。這個主要是時鐘的泄露,采樣時鐘從芯片內部或板上耦合到數據的輸出。

3.2.2數據輸出的隨路時鐘

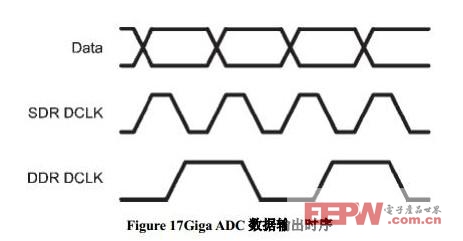

在Giga ADC中,數據的輸出是并行LVDS總線;同時這些總線可以1:2 Demux或者Non-demux;在Non-demux,數據速率和采樣速率是一致的;在Demux模式下,數據速率降低一倍,但數據總線增加一倍。同時,Giga ADC數據輸出的隨路時鐘可以是DDR或SDR,如下圖所示。在Demux和DDR同時使能的情況下,隨路時鐘DCLK只是采樣時鐘的1/4,這個時鐘雜散可能出現在Fs/4的地方。

3.3和輸入相關的雜散

前面提到,和輸入相關的雜散主要是輸入信號的奇偶次諧波混疊進入ADC的第一Nyquist區。這類雜散主要通過外部的抗混疊濾波器加以濾除以及信號輸入端的匹配,差分兩端的平衡來優化。這類雜散在傳統的ADC中已經討論很多,這里就不再贅述。

評論