高性能數字信號處理器TMS320LF2407A及應用

1 引言

本文引用地址:http://www.j9360.com/article/257937.htm數字信號處理器(DSP)已經發展了20多年,最初僅在信號處理領域內應用。近年來, 隨著半導體技術的發展,其高速運算能力使很多復雜的控制算法和功能得以實現,同時將實時處理能力和控制器的外設功能集于一身,在控制領域內也得到很好的應用。數字控制系統克服了模擬控制系統電路功能單一、控制精度不高的缺點,它抗干擾能力強,可靠性高,可實現復雜控制,增強了控制的靈活性。

TMS320LF2407A是美國TI公司推出的新型高性能16位定點數字信號處理器,它專門為數字控制設計,集DSP的高速信號處理能力及適用于控制的優化外圍電路于一體,在數字控制系統中得以廣泛應用 [1]。本文介紹其體系結構、功能特性及其在控制領域中的應用,為數字控制系統的設計提供參考。

2 體系結構和功能特性

2.1 系統組成

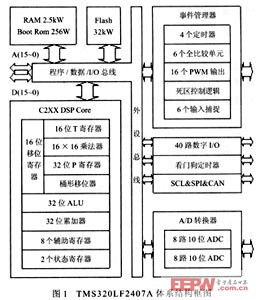

TMS320LF2407A系統組成包括:40MHz、40MIPS的低電壓3.3V CPU、片內存儲器、事件管理器模塊、片內集成外圍設備[2]。其體系結構框圖如圖1所示。

2.2 CPU及總線結構

TMS320LF2407A的CPU是基于TMS320C2XX的16位定點低功耗內核。體系結構采用四級流水線技術加快程序的執行,可在一個處理周期內完成乘法、加法和移位運算。其中央算術邏輯單元(CALU)是一個獨立的算術單元,它包括一個32位算術邏輯單元(ALU)、一個32位累加器、一個16×16位乘法器(MUL)和一個16位桶形移位器,同時乘法器和累加器內部各包含一個輸出移位器。完全獨立于CALU的輔助寄存器單元(ARAU)包含八個16位輔助寄存器,其主要功能是在CALU操作的同時執行八個輔助寄存器(AR7至AR0)上的算術運算。兩個狀態寄存器ST0 和ST1用于實現CPU各種狀態的保存。

TMS320LF2407A采用增強的哈佛結構,芯片內部具有六條16位總線,即程序地址總線(PAB)、數據讀地址總線(DRAB)、數據寫地址總線(DWAB)、程序讀總線(PRDB)、數據讀總線(DRDB)、數據寫總線(DWEB),其程序存儲器總線和數據存儲器總線相互獨立,支持并行的程序和操作數尋址,因此CPU的讀/寫可在同一周期內進行,這種高速運算能力使自適應控制、卡爾曼濾波、神經網絡、遺傳算法等復雜控制算法得以實現。

2.3 存儲器配置

TMS320LF2407A地址映象被組織為三個可獨立選擇的空間:程序存儲器(64K)、數據存儲器(64K)、輸入/輸出(I/O)空間(64K)。這些空間提供了共192K字的地址范圍。

其片內存儲器資源包括:544字×16位的雙端口數據/程序DARAM、2K字×16位的單端口數據/程序SARAM、片內32K×16位的Flash程序存儲器、256字×16位片上Boot ROM、片上Flash/ROM具有可編程加密特性。

TMS320LF2407A的指令集有三種基本的存儲器尋址方式:立即尋址方式、直接尋址方式、間接尋址方式。

2.4 事件管理器模塊

TMS320LF2407A包含兩個專用于電機控制的事件管理器模塊EVA和EVB,每個事件管理器模塊包括通用定時器(GP)、全比較單元、正交編碼脈沖電路以及捕獲單元。

① 通用定時器。TMS320LF2407A共有四個16位通用定時器,可用于產生采樣周期,作為全比較單元產生PWM輸出以及軟件定時的時基。通用定時器有四種可選擇的操作模式:停止/保持模式、連續增計數模式、定向增/減計數模式和連續增/減計數模式。每個通用定時器都有一個相關的比較寄存器TxCMPR和一個PWM輸出引腳T xPWM。每個通用定時器都可以獨立地用于提┮桓鯬WM輸出通道,可產生非對稱或對稱PWM波形,因此,四個通用定時器最多可提供4路PWM輸出。

② 全比較單元。每個事件管理器模塊有3個全比較單元(1、2和3(EVA); 4、5和6(EVB)),每個比較單元各有一個 16位比較寄存器 CMPRx,各有兩個CMP / PWM輸出引腳,可產生2路 PWM輸出信號控制功率器件,其輸出引腳極性由控制寄存器 (ACTR)的控制位來決定,根據需要,選擇高電平或低電平作為開通信號,通過設置T1為不同工作方式,可選擇輸出對稱PWM波形、非對稱PWM波形或空間矢量PWM波形。

死區控制單元 (DBTCON)用來產生可編程的軟件死區,使得受每個全比較單元的兩路CMP / PWM輸出控制的功率器件的間次開啟周期間沒有重疊,最大可編程的軟件死區時間達16μs。

③ 正交編碼脈沖電路。正交編碼脈沖(QEP)電路可以對引腳CAP1/QEP1和CAP2/QEP2上的正交編碼脈沖進行解碼和計數,可以直接處理光電編碼盤的2路正交編碼脈沖,正交編碼脈沖包含兩個脈沖序列,有變化的頻率和四分之一周期(90°)的固定相位偏移,對輸入的2路正交信號進行鑒相和4倍頻。通過檢測2路信號的相位關系可以判斷電機的正/反轉,并據此對信號進行加/減計數,從而得到當前的計數值和計數方向,即電機的角位移和轉向,電機的角速度可以通過脈沖的頻率測出。

④ 捕獲單元。捕獲單元用于捕獲輸入引腳上信號的跳變,兩個事件管理器模塊總共有六個捕獲單元。EVA模塊有三個捕獲單元引腳CAP1、CAP2和CAP3,它們可以選擇通用定時器1或2作為時基,但CAP1和CAP2一定要選擇相同的定時器作為時基;EVB模塊也有三個捕獲單元引腳CAP4、 CAP5和CAP6,它們可以選擇通用定時器3或4作為時基,但CAP4和CAP5一定要選擇相同的定時器作為時基。每個單元各有一個兩級的FIFO緩沖堆棧。當捕獲發生時,相應的中斷標志被置位,并向CPU發中斷請求。

評論