可重構的多DSP圖像并行處理系統

2 可重構數字圖像并行處理系統

2.1 可重構處理系統的組成

可重構計算是指基于可改變(可動態改變)的硬件,以硬件適應算法(即可重構特性)、硬件定制和硬件并行的方式實現計算。可重構處理系統結合了可重構硬件處理單元和軟件可編程處理器,系統允許對可重構處理單元進行配置以滿足不同應用的具體計算要求。

如圖5所示,可重構處理系統的組成基本相同,即通用處理器(陣列)、可重構資源(陣列)、存儲器(陣列)、公用存儲器、系統接口等。面向圖像處理的可重構系統在器件選用上通用處理器可采用適合圖像處理的高性能DSP陣列。

2.2 可重構數字圖像并行處理系統的優點

可重構數字圖像并行處理系統有以下優點:

①FPGA內部的邏輯功能可以在系統運行過程中動態重載,使系統可以實現多DSP之間拓撲的靈活改變以適應各種并行算法的需求,使算法執行效率達到最高。靜態重構和動態重構使系統相比傳統固定系統具有很強的通用性和適應性。

②系統的“多DSP+FPGA”結構能將系統任務劃分成適合FPGA處理的低層信號處理和圖像預處理部分及適合DSP處理的算法,便于發揮兩者的優勢;且 FPGA可通過軟件適應不同時序格式的數字圖像,使得系統具有很高的性能和靈活性。

3 系統設計實例

3.1 系統硬件結構

基于TI公司C6000系列DSP和Xilinx公司Spartan一3系列FPGA,構建基于圖像的點源目標識別系統,對在線可重構數字圖像并行處理系統的可實現性和性能進行驗證。

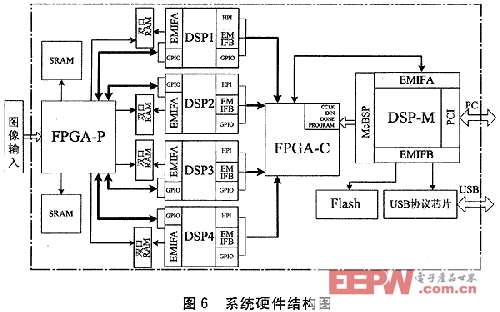

硬件結構如圖6所示。圖像輸入FPGA—P,各DSP分別外擴一片雙口RAM,且將總線EMIFA接到FPGA—P。FPGA—P可用來完成圖像時序處理、圖像數據的轉換、圖像濾波等預處理工作,且可以靈活地將處理后的圖像數據保存到大容量公用數據存儲器SRAM中,并將各DSP訪問的仲裁邏輯或分配保存到各DSP外擴的雙口RAM中。這種結構使系統可以輕松地適應多路圖像輸入。

DSP陣列可以并行完成各種圖像處理算法。FPGA-C建立起DSP間的通信鏈路且暫存各DSP的處理結果。構建通信鏈路的方法有:用FPGA—C在兩 DSP之間構造FIF0或小容量雙口RAM,構建EMIF—HPI通路等。DSP-M可以根據算法需求通過McBSP在線配置FPGA—C,FPGA—C 的配置文件存放在DSP—M外擴的Flash中,這樣就實現了DSP對FPGA的在線可重構。同時,DSP-M擴展了USB、PCI、McBSP等多種接口用來輸出圖像處理結果。

3.2 實驗及結果分析

系統用于實現4路分辨率為256×256、幀頻為50 Hz的8位圖像(如圖7所示)的移動點源目標識別。

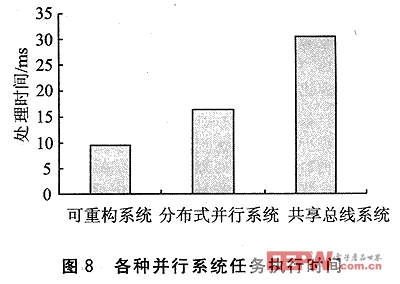

處理過程包括圖像時序采集、轉換,圖像濾波,去除噪聲,姿態融合和目標識別等環節。圖像分配和算法執行所需平均時間僅為9.5 ms。

若用共享總線系統來實現,則多路圖像數據的存儲和分配以及處理器之間的通信將消耗大量時間,大大降低系統效率。若用分布式并行系統來實現,則姿態和多路圖像的綜合處理會給某一個處理器帶來很大的通信量和運算量。將實驗中的圖像處理任務在同等規模的3種系統上分別實現,執行時間如圖8所示。

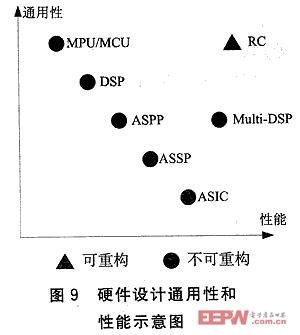

如圖9所示,這些不同形式的計算系統是性能和通用性的不同折衷。可重構算系統代表了介于ASIC和通用處理器之間的計算途徑,在通用性和性能上都優于傳統的硬件系統。圖像處理中數據量大、算法復雜,與其他計算技術相比,可重構計算能充分發揮出效率優勢。可重構系統具有很多優點,但重構延遲和軟硬件劃分問題是應用中需要重點考慮的問題。

結語

傳統固定結構并行圖像處理系統不能適應多種圖像處理并行算法。而可重構數字圖像并行處理系統數據流和結構組織靈活,適于模塊化設計,能大大提高并行算法的執行效率;有較強的通用性,同時其開發周期較短,易于維護和擴展。可重構數字圖像并行處理系統為多媒體圖像處理提供了一個非常有價值的發展方向。

評論