基于DSP與FPGA的高精度數據采集系統設計

當前,許多領域越來越多地要求具有高精度A/D轉換和實時處理功能。同時,市場對支持更復雜的顯示和通信接口的要求也在提高,如環境監測、電表、醫療設備、便攜式數據采集以及工業傳感器和工業控制等。傳統設計方法是應用MCU或DSP通過軟件控制數據采集的A/D轉換,這樣必將頻繁中斷系統的運行,從而減弱系統的數據運算能力,數據采集的速度也將受到限制。本文采用DSP+FPGA的方案,由硬件控制A/D轉換和數據存儲,最大限度地提高系統的信號采集和處理能力。

本文引用地址:http://www.j9360.com/article/257346.htm系統結構

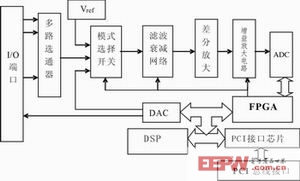

整個采集卡包括信號調理、數據采集、數據處理和總線接口設計。系統結構如圖1所示。

圖1 系統結構框圖

本文設計了具有信號衰減、增益放大和濾波等功能的信號調理電路,采用16位精度、最高采樣率為500KSPS的A/D轉換器AD7676;數字系統設計利用FPGA極其靈活、可編程的特點,選用Altera公司FPGA芯片EP2C8Q208,完成精度校正和邏輯時序控制;DSP采用TI公司的TMS320VC5416,使A/D轉換后的數據在傳輸到上位機之前,進行數據整理、標記、打包以及數據預處理。數據采集卡可同時進行8通道數據采集,通道可進行衰減倍數、采樣速度以及放大增益設置。同時提供模擬輸出通道,用于實現波形產生和模擬驅動功能。能夠進行自動校準,保證數據采集的準確性。PCI總線接口電路采用PLX Technology公司的PCI總線接口芯片PCI9030,完成數據采集和狀態、控制信號的傳輸。

系統硬件電路設計

數據采集模塊設計

從傳感器送來的8路模擬輸入信號通過多路模擬開關ADG507選擇進入模擬通道,如果多通道同時采集,則采用時分復用方式,由FPGA依次控制各通道的通斷。模式選擇開關ADG509為四選一模擬開關,可分別選擇被測模擬信號、標準參考電壓值或用于通道校準的、經過DAC轉換后的信號進入后級濾波衰減網絡電路。送入ADC的信號要先經過低通濾波,以濾除高頻噪聲。濾波電路設計為二階阻容低通濾波器,對頻率高于50KHz的信號濾波。衰減電路設計為有源衰減,選用Linear公司的差分放大器LTC1992,可完成輸入信號極性轉換,實現單端信號轉差分信號,同時通過由FPGA控制繼電器選通不同的電阻網絡調整衰減倍數,可實現對不同電壓輸入范圍信號的調整,以滿足AD7676的輸入電壓范圍。信號增益可編程放大器LTC6911可通過編程設置以1、2、5步進變化的1 V/V100 V/V增益倍數 ,數據采集過程中通過FPGA內部的比較電路自動調整增益放大器增益倍數,極大提高了對微弱信號的分辨能力。AD7676為差分信號輸入, MAX6325基準源提供基準為2.5V的參考電壓,采樣時鐘由晶振提供10MHz時鐘信號經FPGA內部分頻電路得到,單通道最高采樣率為500KSPS。

FPGA電路設計

FPGA芯片也是一種特殊的ASIC芯片,屬于可編程邏輯器件,它是在PAL、GAL等邏輯器件的基礎上發展起來的。同以往的PAL、GAL等相比,FPGA規模比較大,適合于時序、組合等邏輯電路應用。本文選用Altera公司的FPGA芯片EP2C8Q208,完成數據采集卡的時序和地址譯碼電路設計。由于EP2C8Q208有36個M4K RAM,在FPGA內部設計一個16位寬度、4KB深度的FIFO,使用FIFO提高數據采集卡對多通道信號的采集存儲能力。FIFO有半滿、全滿、空標志位,當DSP檢測到半滿標志位時,FIFO同時讀寫;全滿時只讀不寫;空時只寫不讀。A/D采樣控制信號由DSP通過FPGA控制;DSP對采集后的數據進行進一步處理,以提高精度,也具有傳統CPU或MCU的功能,對時序、觸發、DMA中斷請求作出相應處理。

DSP電路設計

DSP采用 TMS320VC5416,它是16位定點DSP,具有高度的操作靈活性和很高的運行速度,采用改善的哈佛結構(1組程序存儲器總線,3組數據存儲器總線,4組地址總線),具有專用硬件邏輯的CPU、片內128KB的存儲器、片內外設,以及一個效率很高的指令集。

DSP 在系統中的作用主要是將A/D轉換后的數據在傳輸到上位機之前,進行數據整理、標記、打包以及數據預處理。數據采集系統所有控制信號都由DSP控制FPGA邏輯電路產生。DSP外掛Flash存放DSP程序及其它配置數據,在上電時,DSP采用并行方式調入DSP內部執行。

評論