復位設計中出現的結構性缺陷及解決方案

本文討論了一些復位設計的基本的結構性問題,在每個問題的最后,都提出了一些解決方案。

隨著數字化設計和SoC的日益復雜,復位架構也變得非常復雜。在實施如此復雜的架構時,設計人員往往會犯一些低級錯誤,這些錯誤可能會導致亞穩態、干擾或其他系統功能故障。

復位域交叉問題

1.問題

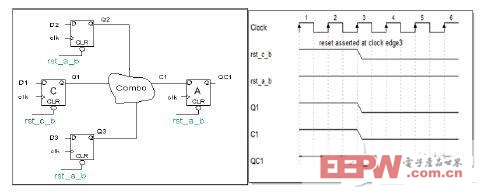

在一個連續設計中,如果源寄存器的異步復位不同于目標寄存器的復位,并且在起點寄存器的復位斷言過程中目標寄存器的數據輸入發生異步變化,那么該路徑將被視為異步路徑,盡管源寄存器和目標寄存器都位于同一個時鐘域,在源寄存器的復位斷言過程中可能導致目標寄存器出現亞穩態。這被稱為復位域交叉,其中啟動和捕捉觸發的復位是不同的。

在這種情況下,C寄存器和A寄存器的起點異步復位斷言是不同的。在C寄存器復位斷言過程中而A觸發器沒有復位,如果A寄存器的輸入端有一些有效數據交易,那么C寄存器的起點異步復位斷言引起的異步變更可能導致目標A寄存器發生時序違規,從而可能產生亞穩態。

圖1:復位域交叉問題

在上面的時序圖中,當有一些有效數據交易通過C1進行時,rst_c_b獲得斷言,導致C1發生異步改變,w.r.t clk從而使QC1進入亞穩態,這可能導致設計發生功能故障。

2.解決方案

*使用異步復位、不可復位觸發器或D1觸發器POR.

*如果復位源rst_c_b是同步的,那么則認為來自C_CLR ——> Q的用于從rst_c_b_reg ——>C_CLR——>C_Q1——>C1——>A_D進行設置保持檢查的時序弧能夠避免設計亞穩態。然而,通常在默認情況下C_CLR——>Q時序弧在庫中不啟用,需要在定時分析過程中明確啟用。

*在目的地(A)使用雙觸發器同步器,以避免設計中發生亞穩態傳播。然而,設計人員應確保安裝兩個觸發器引入的延遲不會影響預期功能。

由于組合環路導致復位源干擾

1.問題

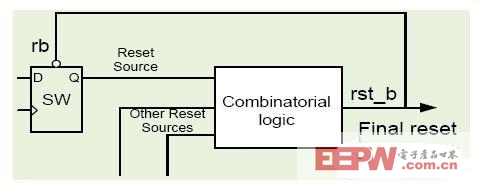

在SoC中,全局系統復位在設備中組合了軟件或硬件生成的各種復位源。LVD復位、看門狗復位、調試復位、軟件復位、時鐘丟失復位是導致全局系統復位斷言的一些示例。然而,如果由于任何復位源導致的全局復位斷言是完全異步的,且復位發生源邏輯被全局復位清零,那么設計中會產生組合環路,這會在該復位源產生干擾。組合路徑的傳播延遲會根據不同的流程、電壓或溫度以及干擾范圍而不同。如果設計中使用了組合信元用于復位斷言和去斷言,那么也會導致模擬中出現紊亂情況。這被視為設計人員的非常低級的錯誤。

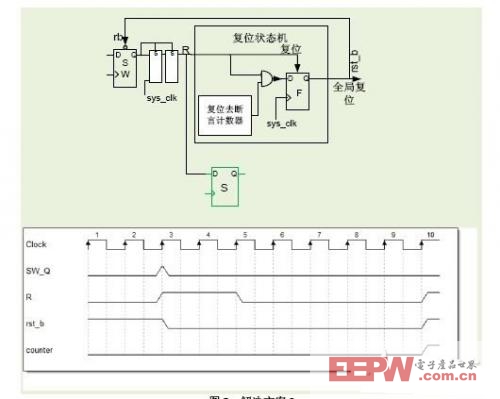

圖2:復位源干擾(基本問題)

在上圖中,當復位源SW_Q斷言時,會導致rst_b斷言,這是全局復位。現在,如果全局復位本身被用于清除“SW_Q”復位斷言,那么會在設計中在SW_Q輸出和全局復位時產生干擾。此外,在模擬中,這會導致紊亂情況,因為復位源斷言試圖通過該組合邏輯去斷言。

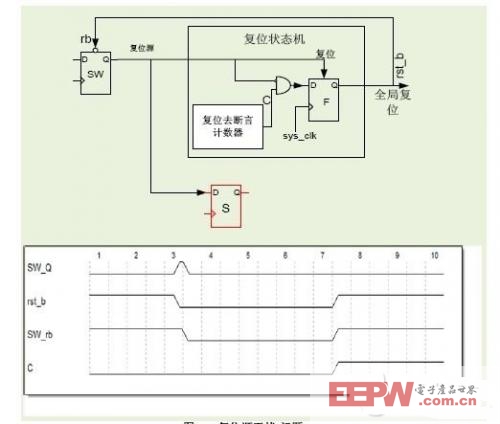

然而,如果復位源(SW_Q)在復位狀態機(觸發器的SET/CLR輸入)為全局復位斷言被異步使用,那么復位干擾可能能夠復位整個系統(通過斷言全局復位),因為全局系統復位去斷言不僅僅與復位源去斷言相關。當該復位源(有干擾)被同步使用或在觸發器D輸入使用的情況下可能依然有一個問題。干擾范圍可能無法在至少一個周期內保持穩定,因此這不會被目標觸發器捕獲。此外,該復位源不能被用作任何電路的時鐘(除了脈沖捕捉電路),因為它可能違反時鐘寬度。

圖3:復位源干擾(問題2)

在上圖中,復位源SW_Q將出現干擾。雖然如果復位源SW_Q的干擾在某個觸發器被捕捉作為復位事件狀態(在S)或用于其他目的,全局復位輸出(rst_b)都沒有干擾,但它將導致時序違反/亞穩態,或根本不可能被捕獲。

2.解決方案

*設計人員永遠都不應犯下上述(圖2)低級錯誤。

*如果復位實現如圖3所示,那么設計人員應保證復位源(在該示例中為SW_Q)總是在觸發器的SET/CLR輸入使用,而不在D或CLK使用。

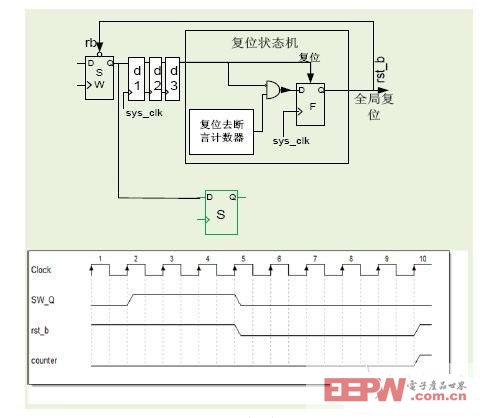

*解決這個問題的最好的方法是在復位狀態機中使用之前注冊該復位源。雖然它將導致時鐘依靠全局復位斷言,但是無論如何,如果沒有時鐘,該內部復位(SW_Q)都不會斷言。請參見圖4.

圖4:解決方案1

此外,用戶也可以擴展SW_Q斷言,然后再在設計中使用它,復位斷言與時鐘無關。請參見圖5.

圖5:解決方案2

評論