復位設計中出現的結構性缺陷及解決方案

冗余復位同步器引起的問題

1. 問題

在使用多個異步時鐘的設計中,設計人員需要確保在目標寄存器使用的時鐘方面,異步復位的同步去斷言,否則可能導致目標觸發器發生時序違反,從而產生亞穩態。復位同步器被用來復位去斷言,與目標時鐘域同步。然而,只有在系統復位去斷言過程中有目標時鐘時才會發生復位去斷言時序違反。如果在復位去斷言時沒有時鐘,那么便不會有任何時序違反。因此,在設計多時鐘域模塊時,設計人員可以讓編譯時間選項繞過該模塊中的那些復位同步器,并讓系統集成商根據對該模塊的時鐘可用性決定是否需要使用復位同步器。

此外,如果系統時鐘和異步時鐘比非常高,冗余同步器甚至會造成設計功能性問題。下面描述了這個問題。

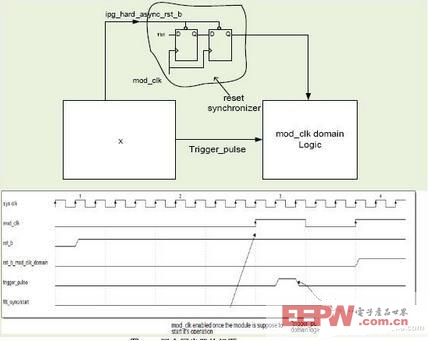

圖12:冗余同步器的問題

在上面的設計中,去斷言與sys clk同步的系統復位被饋送到(mod_clk域)的復位同步器,然后在mod_clk域邏輯中使用該復位。讓我們假定sys clk : mod_clk的時鐘頻率比大于6:1.默認不啟用mod_clk,以節省動態功率。當用戶想要啟用mod_clk域邏輯的功能時,便啟用該時鐘。在啟用了該時鐘后,有兩個mod_clk周期的延遲,其中,由于復位同步器導致整個mod_clk域邏輯都處于復位狀態。在該階段,如果一些數據交易從sys clk域開始,將在mod_clk域丟失。

2. 解決方案

雖然這不是大問題,但有時會在客戶一端造成混淆,因為該延遲對客戶不可見。 因此消除混淆的更好的方式是:

* 如果在全局復位去斷言過程中沒有時鐘,則在設計中繞過/刪除冗余復位同步器。 這當然會節省一定的門控數。

* 如果動態功耗不是問題,用戶可以在mod_clk域邏輯開始運作之前很長時間在啟動代碼選擇啟用mod_clk. 因此,復位去斷言將有足夠的時間傳播。

* 這也可以在軟件中處理,在任何有效操作之前啟用了mod_clk后,設置兩三個mod_clk周期的延遲。

由于罕見的時鐘路徑導致復位去斷言時序問題

1. 問題

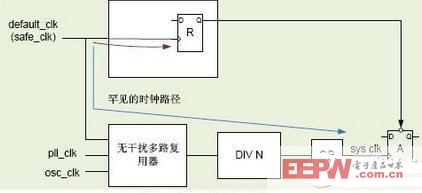

設計的復位架構根據系統而不同。在一些安全關鍵設備中,整個復位狀態機在安全時鐘上工作,安全時鐘默認啟用。 該時鐘也被用作設備的默認系統時鐘。

圖13:罕見時鐘路徑的問題

在上圖中,復位狀態機(R觸發器)在default_clk上工作。此外,在復位去斷言過程中,default_clk是sys clk的源。因此,在邏輯上,這兩個時鐘(clk1和clk2)在復位去斷言過程中同步。但是,由于clk1和clk2之間存在巨大的罕見路徑,因此很難平衡這兩個時鐘并視其為同步。 因此,滿足A觸發器的復位去斷言變得具有挑戰性。

2. 解決方案

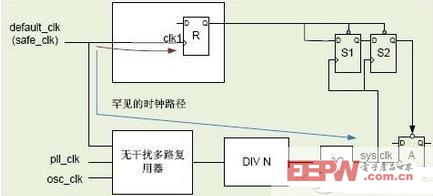

異步對待clk1和clk2,并在A觸發器中使用復位之前放置復位同步器。現在需要從S2--》A滿足復位去斷言時序(見圖14)。這不應是個問題。

圖14:解決方案

結束語

本文主要專注于復位設計中的故障以及克服這些問題的可能的解決方案,然而,上述解決方案并非唯一的解決方案,也不普遍適用于所有設計。這些是一些通用的解決方案和建議的指導方針,在特殊情況下可能需要進行修改。

評論