一種DSP內嵌DARAM的電路設計與ADvance MS仿真驗證

摘要:介紹了一種DSP芯片內嵌DARAM的電路結構,詳細分析了接口電路中各個模塊的功能,包括地址譯碼電路,字線譯碼電路,位線選擇電路及控制電路四部分內容。著重介紹了控制電路的原理,及如何實現一個周期“雙存取”的功能。利用數模混合仿真工具ADvance MS對整體電路進行仿真,結果證明DARAM可以在一個時鐘周期內完成一次讀和一次寫操作,實現預期的功能,為DSP設計乃至SOC的設計工作提供了參考。

本文引用地址:http://www.j9360.com/article/255835.htm在復雜的系統級微處理器設計中,存儲器負責系統程序和數據的儲存,是整個系統的重要組成部分,在CPU執行指令的過程中,要經常被訪問存儲器,所以存儲器的讀寫速度會影響指令執行的速度。RAM是系統芯片中常用的存儲器,用來存放數據,普通的RAM在一個時鐘周期內只能進行一次讀或寫操作,即CPU在一個時鐘周期內只能訪問存儲器一次,稱為單存取隨機存儲器(Single-Access On-Chip RAM),而雙存取隨機存儲器(Dual-Access On-Chip RAM)可以在一個吋鐘周期內進行數據的讀和寫兩次操作。利用DARAM一個周期內“雙存取”的特點,可以大幅提高CPU執行指令的速度,進而提高整個系統的性能。

1 DARAM整體電路

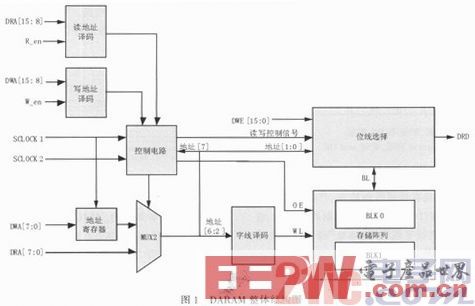

DARAM整體電路如圖1所示,該DARAM的大小為256字x 16位,用來存儲數據,輸入信號為兩相不交疊時鐘SCLOCK1和SCLOCK2,數據寫總線DWE,數據讀地址總線DRA和數據寫地址總線DWA,讀使能R_en和寫使能W_en(高電平有效),輸出信號為數據讀總線DRD。

DARAM的存儲陣列根據地址的高低分為大小相等的兩塊,接口電路主要包括地址譯碼、地址選擇、字線譯碼、位線選擇和控制電路幾個部分。其中,控制電路中的讀寫使能信號與內部時鐘共同作用產生的脈沖信號,會使地址選擇電路在一個時鐘周期內的高低電平部分,分別輸出讀地址和寫地址,這樣就可以使位線選擇電路在一個周期內進行讀寫兩次操作,這是接口電路中的重要部分,也是隨機存儲器可以進行“雙存取”的關鍵。

2 DARAM電路設計

2.1 地址譯碼

該DARAM的物理地址為0300H-03FFH,所以讀寫地址的高8位必須為“0000_0011”,地址譯碼電路的功能就是判斷高8位地址是否匹配,如果地址匹配W_en和R_en才會輸入到控制電路。

2.2 控制電路

控制電路實現的功能有:產生內部時鐘,讀寫脈沖信號和預充電控制信號OE。

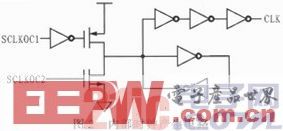

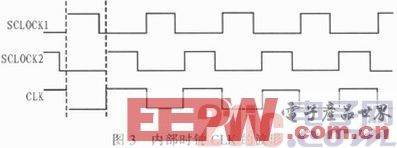

圖2中SCLOCK1和SCLOCK2高電平不交疊,當SCLOCK1為高時輸出0,SCLOCK2為高時輸出1,都為低時輸出保持不變,這樣兩相時鐘就轉換成一相內部時鐘CLK,如圖3。

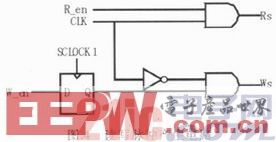

圖4產生的讀寫脈沖信號Rs與Ws會控制地址選擇模塊。W_en經過一個高電平觸發的觸發器,是為了寄存半個周期的時間,使輸出的讀脈沖Rs和寫脈沖Ws交替產生,形成單周期雙脈沖,是可以實現“雙存取”的關鍵。

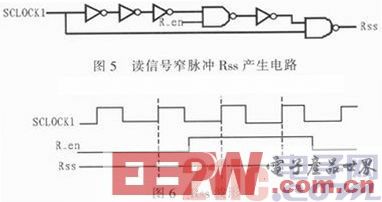

圖5電路中,當進行讀操作時,R_en為高,在時鐘上跳的瞬間,由于邏輯門的延遲,輸出信號會出現一小段低電平,之后再升高,這樣就產生了一個很窄的脈沖Rss,見圖6。類似的,由SCLOCK2和W_en也會產生寫信號窄脈沖Wss。

Rss與Wss并不是最后控制讀寫放大器的控制脈沖,因為讀出與寫入數據的時間很關鍵,也就是說脈沖的寬度要很精確,讀脈沖如果過寬的話不僅會增大靈敏放大器的能量消耗,也會減慢數據讀出的速度,時間要恰好使位線上的電壓可以滿足靈敏放大器的靈敏度,而寫脈沖如果太窄,數據會無法寫入,所以要設計的恰到好處。

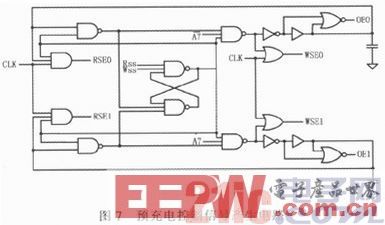

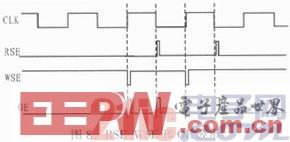

圖7所示電路可以產生讀寫控制脈沖和預充電控制信號。RSE是讀脈沖,WSE是寫脈沖,OE是預充電控制信號,由讀寫地址的第7位A7選擇要控制的存儲塊。負載電容的大小就決定了讀寫脈沖的寬度,所以需經過精確設計。最終輸出的波形如圖8。

2.3 地址選擇

由控制電路產生的Rs和Ws會控制DRA和DWA低8位的傳輸,使兩條地址總線有選擇性的輸出,產生一條8位的讀寫地址總線,其中地址[1:0]經過譯碼會控制四條位線,進行位線選擇,地址[6:2]會進行字線譯碼,地址經過控制電路產生存儲陣列的塊選擇信號。

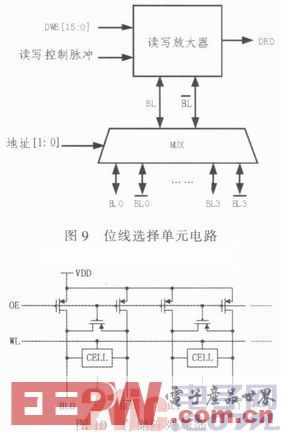

2.4 位線選擇與存儲陣列

位線選擇電路包括讀寫放大器和多路選擇器。圖9為一個位線選擇單元,根據最低兩位數據地址來選擇4組位線,由讀寫控制脈沖RSE和WSE決定對位線進行讀或寫操作。這就意味著在一個周期內,并不是對任意兩個讀寫地址都可以進行操作,也就是說,進行“雙存取”的兩個地址必須相近,這也是可以實現“雙存取”的關鍵。

存儲器相關文章:存儲器原理

脈沖點火器相關文章:脈沖點火器原理

評論