航天器電子設備電磁兼容性設計

摘要:針對小衛星平臺某電子設備內部電磁環境,給出了電磁兼容性(EMC)設計原則和具體方法,包括結構設計、屏蔽設計、濾波設計及PCB板設計等,EMC試驗表明該設備電磁兼容設計合理,這對星載電子設備的電磁兼容設計有較高的參考價值。

本文引用地址:http://www.j9360.com/article/249782.htm隨著電子技術應用的日益發展,電子設備越來越復雜,電磁環境日趨惡劣,它影響了電子設備和系統的正常工作和性能。一個性能好的電子產品必須考慮電磁兼容問題,既不能有電磁輻射干擾其他電子設備的正常工作,又要具備較低的敏感度,能抵抗規定的電磁干擾。

航天器電子設備對體積,質量和功耗的限制是十分苛刻的,而對產品高性能的追求也是不斷提高。某電子設備是適應小衛星平臺小型化、集成化的需求,將多種功能線路組合在一起,設備內部干擾源和敏感器件多,信號傳輸線多,空間小,相互間很容易造成干擾。如果干擾效應嚴重,將導致系統失靈,甚至可能產生嚴重的故障,所以電磁兼容性是該設備的一項重要指標。

1 電磁兼容性與電磁干擾

電磁兼容性(EMC)是指電子設備在預期的電磁環境中能夠協調、有效地進行工作的能力。其目的是使電子設備既能抑制各種外來的干擾又能減少其本身對其他電子設備的電磁干擾。電磁干擾(EMI)可理解為一種有損于有用信號的電磁現象,干擾的來源主要有本電子設備內部形成的干擾以及外界耦合到本電子設備形成的干擾。

電磁兼容主要解決的是電子、電氣設備或系統間的電磁干擾問題,構成電磁干擾必須具備3個因素,即干擾源、受干擾對象(敏感設備)及兩者間耦合路徑。電磁干擾的基本模型就是這3個因素的串聯,如圖1所示。

系統或設備內部要發生電磁兼容性問題,必須同時存在以上3個因素,在解決電磁兼容問題時,要從這3個因素入手,消除其中某一個因素,就能解決問題。對新研制的電子設備,應該從設計開始階段就考慮電磁兼容,進行電磁兼容設計。在設計階段就考慮電磁兼容,遠比制作成型后再試圖滿足電磁兼容標準要求而采取措施更節省人力和物力。所以電子設備必須在產品設計階段就要考慮電磁兼容問題。

2 某星載電子設備簡介

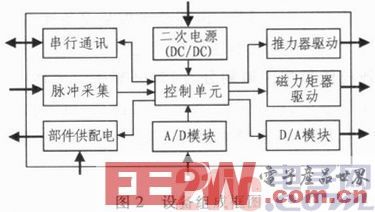

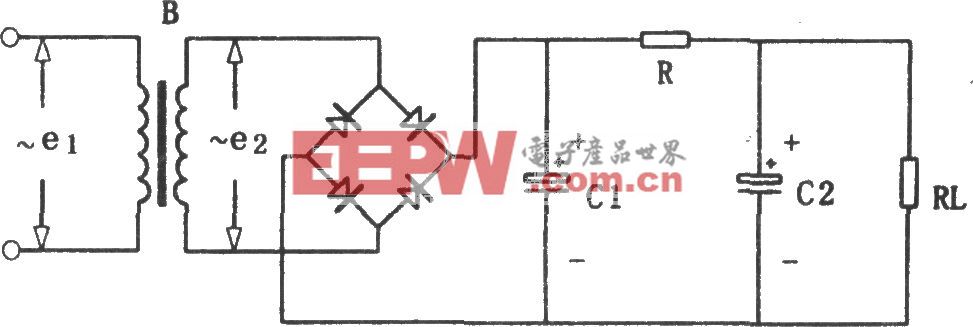

小衛星平臺某電子設備是衛星的主要控制器之一,如圖2所示。

以處理器控制單元為中心,外圍包括DC/DC模塊、串行通訊模塊、推力器驅動模塊、磁力矩器驅動模塊、供配電模塊等單元。設備內既有DC/DC、部件供配電、推力器驅動等強干擾源信號,又有A/D和D/A輸入輸出小信號,同時還存在高速脈沖輸入信號,以及控制單元內部的高速時鐘信號。因而設備內部的電磁環境很復雜,電磁兼容性成為該設備的一項重要設計內容,結果的好壞直接影響產品的性能。

3 電磁兼容性設計

3.1 結構與地線設計

本星載電子設備采用無線纜機箱結構,相對傳統電纜結構機箱,無線纜機箱能大大減少電磁干擾,這是因為80%的EMC問題是因電纜造成,電纜是高效的電磁波接收天線和輻射天線,同時也是干擾傳導的良好通道。如圖3所示,設備采用雙總線板結構,通過內總線板實現設備內部各功能板之間的信號傳遞,通過內總線板與外總線板之間的“大芯數轉接內電連接器”以及外總線板上的“焊針型直插印制板電連接器”實現內部信號與設備外部信號之間的傳遞。

機箱結構設計時,將強弱信號所在的線路板分開進行合理布局,易產生電磁干擾的線路板設置在機箱的上下側邊,使產生的干擾信號能通過機箱外殼釋放,數字等敏感信號處理線路板放置在機箱中部,二次電源模塊是主要的干擾源,由主備份兩塊線路板組成,正常工作時使用主份,所以將份板放在機箱最外側,備份二次電源板平常不工作,成為一道屏障阻止主份二次電源板產生的干擾信號向機箱內輻射。

設備內部的地線包括一次地、數字地和模擬地,其中數字地和模擬地屬于二次地。設計時將數字地和模擬地分開布線,在設備內進行單點連接,一次地與數字地和模擬地進行嚴格隔離,避免單機接地故障為一次電源帶來致命的危害從而影響整星的正常工作。內外總線板是設備強弱信號輸入輸出通道,為遏制和減小這些信號之間的干擾,將內外總線板上的強弱信號按區域劃分,同時分割相應的地層,由于地線層處處等電位,不會產生共模電阻耦合,也不會經地線形成環流產生天線效應,使電磁干擾能以最短的路徑進入地線而消失。

3.2 濾波與屏蔽

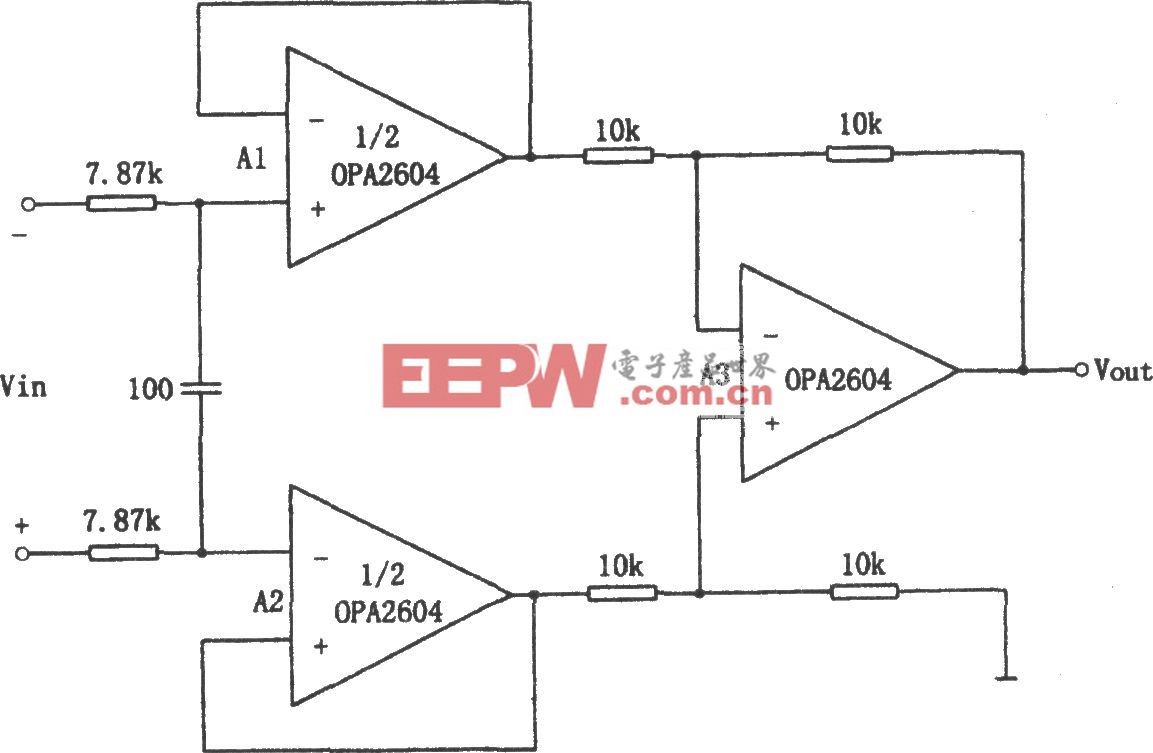

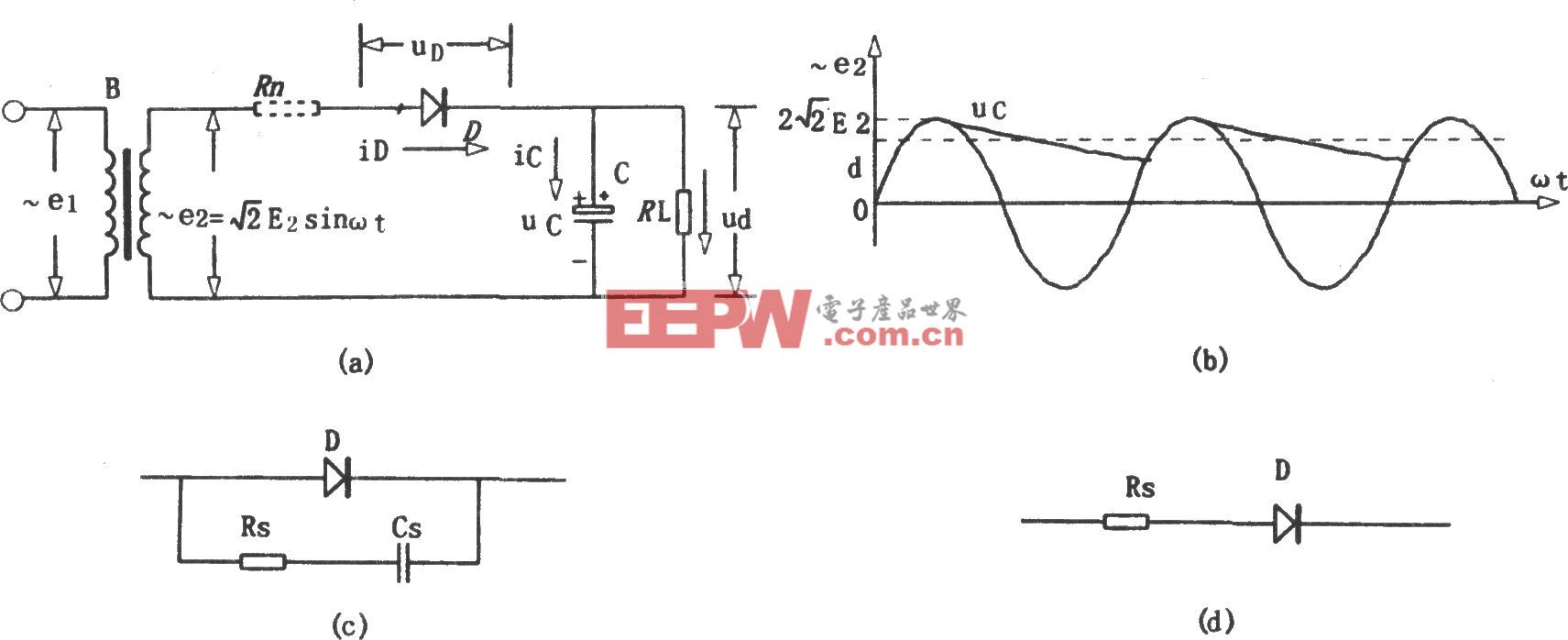

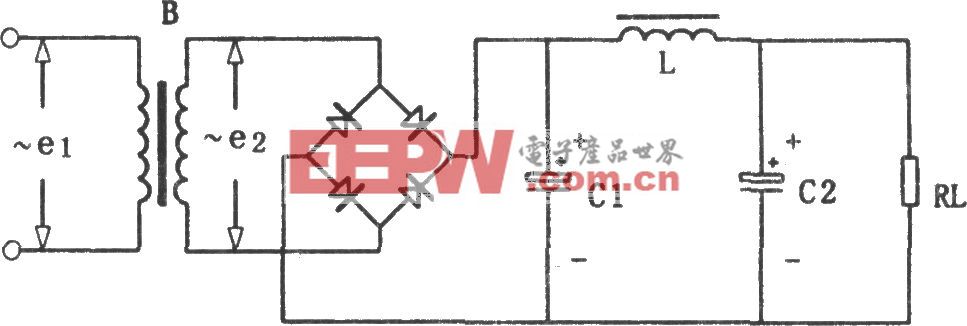

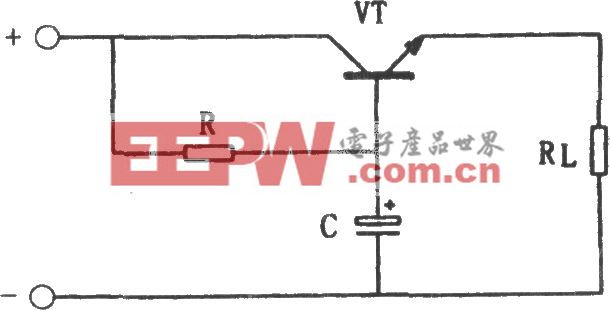

濾波的功能是讓指定頻率范圍內的信號通過,而將其他頻率信號加以抑制。它是減弱傳導干擾和輻射于擾最常用手段之一,特別是對瞬態干擾的抑制更有效。本星載電子設備的濾波設計主要是對DC/DC電源模塊濾波和對線路去耦電容濾波。

在DC/DC模塊的輸入濾波電路主要由一級∏濾波和兩級LC濾波電路組成,采用差模和共模組合式濾波措施,能有效阻止來自電源母線的噪聲干擾,同時阻止DC/DC電源本身產生的開關噪聲反饋到一次母線內阻上,形成公害。

在設計印制電路板時,通過在電路上加去耦電容來滿足數字電路工作時要求的電源平穩和潔凈度。去耦電容的充放電作用使集成芯片得到的供電電壓比較平穩,減小了電壓振蕩現象,集成芯片可以就近在各自的去耦電容上吸收或釋放電流,而不必通過電源線從較遠的電源中取得電流。因此不會影響集成芯片的速度,同時去耦電容為集成芯片的瞬態變化電流提供了各自就近的高強通道,從而大大減小了向外的輻射噪聲,且相互之間沒有公共阻抗,因此抑制了共阻抗耦合。

設計時在每個集成芯片的電源和地腳之間加一個0.01~0.1 μF去耦電容,有效去除信號線中的高頻噪聲。在每塊線路板電源輸入端接一組5 μF電容和一組0.01μF電容,濾除電源線上的高頻干擾和低頻噪聲。

評論