基于PCI總線加密卡硬件設計

3.1 3DES算法模塊設計

本設計采用兩個密鑰的3DES,該加密方案使用兩個不同的密鑰Key1和Key2對明文進行三次DES或DES-1變換,加密函數采用加密-脫密-加密序列:

兩個密鑰的三重DES的有效密鑰長度是112位。在本設計中采用了密碼分組鏈接方式(CBC)。在這種方案中,加密算法的輸入是當前的明文分組和前邊的密文分組的異或,對每個分組使用相同的密鑰。從效果上看,將明文分組序列的處理連接起來了。每個明文分組的加密函數的輸入與明文分組之間不再有固定的關系,因此,64bit的重復模式不再會暴露。

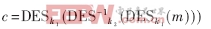

3DES密碼硬件模塊為控制模塊和數據路徑設計兩部分。控制模塊產生數據通路需要的控制信號序列,保證數據處理單元正確有序地工作。數據路徑用來實現信息傳送和密碼變換的數據處理單元。3DES算法設計采用迭代結構,由初始置換電路IP、多路選擇電路L_MUX和R_MUX、32-bit L鎖存器、32-bit R鎖存器、擴展置換E處理電路、S盒數據代替電路、P盒置換電路及末置換IP-1電路構成。其運算電路如圖3所示。

3.2 3DES輸入輸出模塊設計

輸入輸出模塊主要為密碼運算模塊提供密鑰、數據以及命令信息的模塊。控制信號主要包括:操作時鐘CLK、系統初始化INIT、寫使能WEN、讀使能REN、運算完畢READY、DIN[31:0]、數據輸入、數據輸出DOUT[31:0]、端口選擇A[2:0]。當INIT=1時,將3DES模塊內部所有寄存器復位并清零;當A[2:0]=010, WEN=1時,在CLK時鐘上升沿,將命令字由32位數據總線寫入芯片內部命令寄存器;當A[2:0]=001,WEN=1時,在CLK時鐘上升沿,將128位的密鑰分四次由32-bit數據總線寫入芯片內部密鑰寄存器;當A[2:0]=000,WEN=1時,在CLK時鐘上升沿將64位的數據分兩次由32位數據總線寫入芯片內部輸入數據寄存器;每寫夠2個長字,3DES模塊開始運算,運算完畢后,READY變為高電平,輸出數據分為兩組分別送入temporary_l和temporary_2兩個寄存器。3DES Quartus仿真波形如圖4所示。

評論