基于DSP與CPLD的I2C總線接口的設計與實現

如今,為了提高系統的數據處理精度和處理速度,在家用電器、通訊設備及各類電子產品中已廣泛應用DSP芯片。但大多數的尚未提供I2C總線接口,本文將介紹一種基于CPLD的已實現的高速DSP的I2C總線接口方案。

1 I2C通信協議

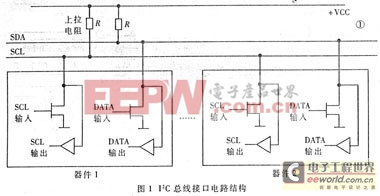

I2C總線是一種用于IC器件之間的二線制總線。它通過SDA(串行數據線)及SCL(串行同步時鐘線)兩根線在連到總線上的器件之間傳送信息,通過軟件尋址實現片選,減少了器件片選線的連接。CPU不僅能通過指令將某個功能單元電路掛靠或摘離總線,還可對該單元的工作狀況進行檢測,從而實現對硬件系統的擴展與控制。I2C總線接口電路結構如圖1所示,I2C總線時序圖如圖2所示。

|

|

I2C總線根據器件的功能通過軟件程序使其可工作于發送主或接收從方式。總線上主和從即發送和接收的關系不是一成不變的,而是取決于數據傳送的方向。SDA和SCL均為雙向I/O線,通過上拉電阻接正電源。當總線空閑時,兩根線都是高電平。連接總線的器件的輸出級必須是集電極或漏極開路的,以具有?quot;與"功能。I2C總線的數據傳送速率在標準工作方式下為100kbit/s,在快速方式下,最高傳送速率可達400kbit/s。

在數據傳送過程中,必須確認數據傳送的開始和結束信號(也稱啟動和停止信號)。當時鐘線SCL為高電平時,數據線SDA由高電平跳變為低電平則定義為"開始"信號;當SCL為高電平時,SDA由低電平跳變為高電平則定義為"結束"信號。開始和結束信號都由主器件產生。在開始信號以后, 總線即被認為處于忙狀態;在結束信號以后的一段時間內,總線被認為是空閑狀態。

在I2C總線開始信號后,依次送出器件地址和數據,I2C總線上每次傳送的數據字節數不限,但每一個字節必須為8位,而且每個傳送的字節后面必須跟一個認可位(第9位),也叫應答位(ACK)。從器件的響應信號結束后,SDA線返回高電平,進入下一個傳送周期。關于I2C總線協議的詳細說明請參看參考文獻。

2 設計方案

本文以DSP芯片ADSP21992與時鐘芯片PCF8583的控制接口為例,說明基于CPLD的I2C總線接口設計方案。

ADSP21992是2003年最新推出的160MIPS、帶CAN通信接口的適合于高精度工業控制和信號處理的高性能DSP芯片。它帶有48K片內RAM、SPORT通信接口、SPI通信接口、8通道14位A/D轉換器以及PWM等。關于ADSP21992的詳細說明請參看參考文獻。

評論