基于SmartFusion2的溫度采集系統簡單應用設計

0 引言

本文引用地址:http://www.j9360.com/article/236575.htmInternet的快速發展和成功促進了以太網(Ethernet)技術的發展和應用的擴展,所涉及的領域十分廣泛,如傳統的工業控制、信息家電、智能家居、安全監控、樓宇自動化、醫療、環境監測等。大多數的數據采集設備的通信接口符合UART 通信標準。這種通信方式的數據傳輸半徑十分有限,并不能滿足遠距離傳輸的需求,并且不能接入Internet.因此數據的交互接入Internet 就顯得非常重要了。

1 系統的總體方案及各主要模塊設計

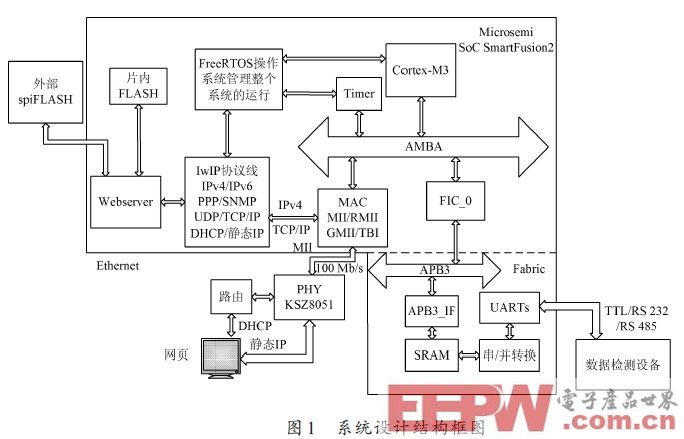

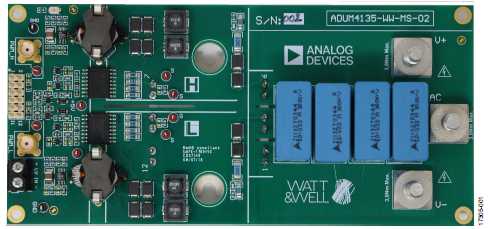

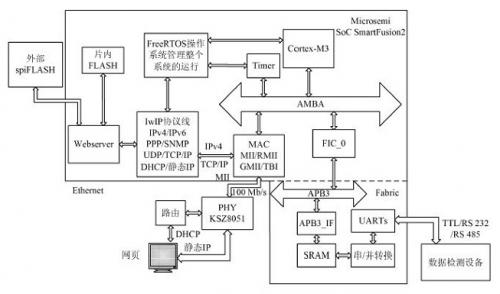

系統以Microsemi(Actel)公司的基于FLASH 架構的SoC FPGA 產品SmartFusion2器件為核心[1].系統通過Fabric架構實現多路UART對外相應數據進行采集,進行并/串轉換寫入Fabric 的雙端口RAM.SmartFu-

sion2的ARM Cortex-M3子系統經過AHB/APB總線矩陣以AHB/APB 方式訪問Fabric 的RAM,將得到的數據經過Ethernet以網頁的形式在PC上顯示。反之,以同樣的路徑將主控的指令傳輸到外部的終端設備。PC機端以網頁形式實現數據交互。網頁存放于SmartFusion2 內部FLASH,內核Cortex-M3 基于實時操作系統(FreeR-

TOS)管理任務,IP 采用靜態方式,內核Cortex-M3 與Fabric采用AHB方式通信[2-3].系統設計結構框圖如圖1所示。

系統硬件的設計可分為三個主要模塊,分別為PHY 物理層模塊,SoC 的Cortex-M3 內核及FPGA 系統,UART模塊的數據采集系統。

1.1 PHY模塊

PHY 即物理層(Physical Layer)。物理層協議可定義電氣信號標準、連線的狀態、時鐘信號的要求、數據編碼的格式和數據傳輸所用的連接器等。物理層通過一個定義好的接口與數據鏈路層進行通信。比如MAC 可以利用標準的介質無關性接口( MII接口)與PHY進行數據交換通信。PHY還有個重要的功能就是實現以太網的CSMA/CD 部分功能,這是硬件上實現的。它可以檢測到網絡鏈路上是否有數據正在傳送,如果有數據在傳送中則進行等待,當檢測到網絡空閑,就再等待一定的時間(不同的PHY會有不同)后對數據進行傳送。倘若兩塊網卡碰巧是同時發送數據,這將造成沖突,這時PHY 內部的沖突檢測結構可以檢測到沖突的發生,然后兩邊各自等待一定的時間進行重發數據。

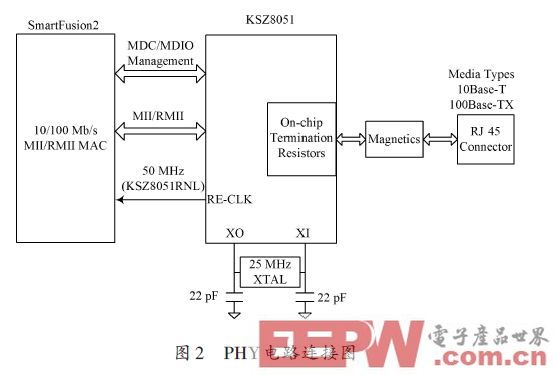

PHY 的電路圖連接圖如圖2 所示。KSZ8051 采用MII與SmartFusion2相連,由于MII兼容RMII接口,因此程序也可配置為RMII模式。Management采用2個引腳連接,分別為MDC 和MDIO,MII 的時鐘由PHYKSZ8051 提供,KSZ8051 的時鐘來自外部25 MHz 晶振。媒體連接采用RJ 45,兼容10 Mb/s和100 Mb/s.

1.2 SoC中的Cortex-M3模塊

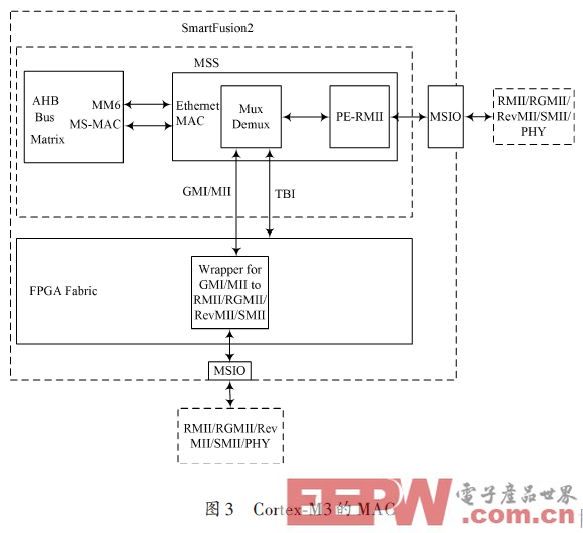

系統使用Cortex-M3 中的MAC 模塊,如圖3 所示。

通過AHB控制Ethernet MAC模塊,對于MAC的配置是使用其內部的寄存器,可以配置不同的接口模式,不同的速度。本系統配置為MII接口,100 Mb/s速度。

MAC(Media Access Control,媒體訪問控制子層協議),主要負責控制和連接物理層。在發送數據的時候,MAC 協議可以事先判斷現在是否可以發送數據,如果可以發送則將給數據加上一些控制信息,最終將數據及附帶的控制信息以規定的格式發送到物理層;在接收數據的時候,MAC 協議首先判斷輸入的信息是否發生傳輸錯誤,如果沒有錯誤,則去掉控制信息發送至邏輯鏈路層(LLC)層。以太網MAC 協議由IEEE 802.3以太網標準定義。

PHY 與MAC 的接口方式有多種,如:

MII,RMII,SMII,SSMII,GMII,SGMII,TBI等。目前常見的PHY都提供標準的MII接口,RMII信號是對PHY內部的MII的信號進行編碼和解碼,這就是說支持MII接口的PHY 內部都含有RMII 信號,也就是支持RMII接口。具體使用何種接口的PHY則必須根據MAC 芯片對應的功能和接口的標準來決定。

采用FreeRTOS 實時操作系統管理整個系統的運行。FreeRTOS使用Cortex-M3內核的定時器以10 ms時間片進行任務的調度和切換。創建WebServer進程和網頁進行通信,網頁編輯語言HTML 是不需要編譯的,因此將需要顯示的數據全部發送給網頁。這些數據存儲在FLASH中,目前測試是存儲在片內FLASH,網頁發來的控制數據進行實時的處理。網頁的數據需要用LwIP協議棧進行打包,LwIP 協議棧是把所有的協議封裝到一個單一的過程(進程)中,從而與操作系統內核分開。應用程序可能也駐留在LwIP 處理過程中,或者在單獨的過程中。TCP/IP棧和應用程序之間的通信可以通過函數調用實現,也可以通過更為抽象的API[4-5].本設計的應用層使用常用的IPv4 協議,DHCP和靜態IP 都進行測試,傳輸層和網絡層使用TCP/IP.

打包之后的需要介質層MAC 進行處理,此MAC 為Cor-

tex-M3 內核自帶的,支持多種MAC 接口,本設計采用MII接口,所采用的PHY芯片也是MII接口,采用Micrel公司的KSZ8051,支持MII、RMII 接口,10 Mb/s 和100Mb/s傳輸速度,設計時采用100 Mb/s傳輸。

網頁的數據需要實時更新,設計網頁每隔500 ms發一次更新的命令,Cortex- M3再將更新的數據發送給網頁。而這些數據來自APB3上,Cortex-M3通過FIC_0和APB3 進行雙向通信,從而發送和接收數據。FPGA中Fabric 和APB3 進行雙向通信,數據存儲在雙端口SRAM 中,多路UART 和SRAM 進行雙向通信。SRAM在系統起緩存的作用,用來解決兩端讀寫速度的不同。

而對于UART的數據也定義了協議,這些協議是區分數據的格式和內容。對于UART的個數可以進行增加,系統UART的同步使用FPGA硬件實現,不受個數的限制。

1.3 FPGA的UART模塊

本系統的主要功能是UART數據的采集與交互,使用網頁進行人機交換,實現數據的實時更新和控制,并且把采樣點的采樣時間也傳輸過去,使用戶知道數據的具體時間,便于以后的查看。

在本設計中需要在SmartFusion2片內的FPGA部分設計多路串口數據采集與存儲的控制器,實現對終端的多路串口數據進行采集。使用的多路串口數據采集方法是在SmartFusion2片內的FPGA中設計一個UART控制器去采集多路數據[6].控制器并不完成串轉并控制,而是實時監測多路串口數據狀態,并將多路串行數據實時切換送入RAM控制器,串行的數據經過RAM控制器串行的進入RAM中去。如圖4所示。

晶振相關文章:晶振原理 溫濕度控制器相關文章:溫濕度控制器原理

評論