提高加密應用的系統效率

為了確保數據從數據源安全傳輸到目的地,必須在安全應用中采用加密技術。最常用的加密技術采用確定性算法,并對固定長度數據塊進行固定不變的轉換操作。此類加密技術包括高級加密標準(AES)、數據加密標準(DES)、國際數據加密算法(IDEA)和RC5等。

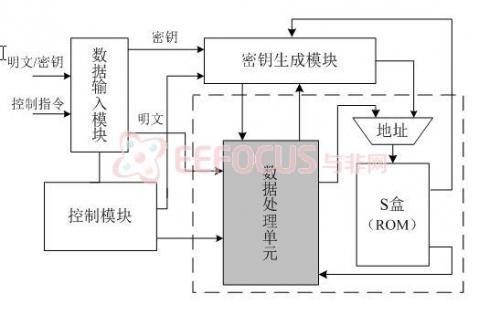

本文引用地址:http://www.j9360.com/article/235667.htm然而,這種“分組密碼”方案會制約硬件的吞吐量、數據處理和緩沖容量,因為加密操作必須在下個數據塊到來之前完成。大量工業加密系統都支持200Mbps以上的數據速率,但與簡單的微控制器相比,硬件(一般是ASIC)要想達到如此高的數據速率所需的成本極高。盡管簡單地利用具有外部存儲器的8位MCU(例如8051)能夠實現加密功能,但執行加密所用的時間與ASIC相比就會呈數量級增加。本文將介紹如何利用帶可編程邏輯的SoC并借助MCU內核以及通用數字塊(UDB)和直接存儲器訪問(DMA)等其它硬件功能來實現加密并改善系統的總體時間。

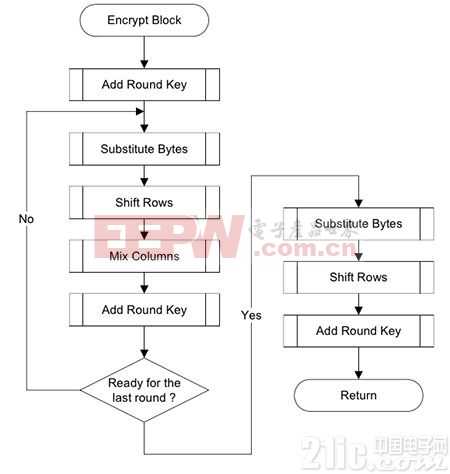

高級加密標準(AES)是最常用的分組密碼技術之一,采用對稱密鑰密碼。我們以AES-128器件通過128位加密密鑰處理16字節(128位)數據塊為例,演示加密應用的要求以及可能的實現方案。在處理開始之前,利用AES-128將輸入字節設置成圖1所示的分組格式。表中的in0是第一個字節,in15是第16個字節也是輸入塊的最后一個字節。

評論