集成電源噪聲抑制的時鐘源簡化FPGA系統的電源設計

圖1(a)的小數分頻拓撲圖是由一個晶體振蕩器、模擬鑒相器、模擬補償濾波器、模擬VCo和一個小數分頻反饋分頻器組成。輸出頻率等于輸入頻率的N倍。低噪聲緩沖器用于驅動外部負載電路。許多應用程序,例如千兆以太網、光纖通道以及高清晰度串行數字視頻(HD-SDI)信號,依靠輸出頻率在100Hz~156.25MHz范圍的低抖動時鐘源。在理想的供電條件下,小數分頻PLL可在1 0kHz~20MHz頻段內提供低于lps RMS的抖動性能。相反,在有電源噪聲的環境中,振蕩器很難滿足其數據手冊中標明的相位抖動參數。使用模擬子電路構建的節點非常敏感,極易受到噪聲的影響。當噪聲進入系統,它通常會放大并輸出相位抖動。

6 Silicon Labs DSPLL時鐘產品解決方案

相比之下,Silicon Labs DSPLL使用數字處理技術實現PLL,通過倍乘晶體參考頻率得到更高的輸出頻率,晶體不會受到干擾。其次,所有頻率控制和增減使用數字命令進行處理。補償濾波器基于數字信號處理器,沒有使用電容器或其他被動元件。最后,VCo使用數字控制,而不是模擬電路。為了提供額外的VDD隔離,片上線性穩壓器和集成的電源去耦電容用來進一步確保噪聲抑制。由于這些優勢,即使在嘈雜的環境中,每個Silicon Labs的基于DSPLL技術的XO/VCXO都有能力產生具有亞皮秒級抖動性能的高頻時鐘信號。

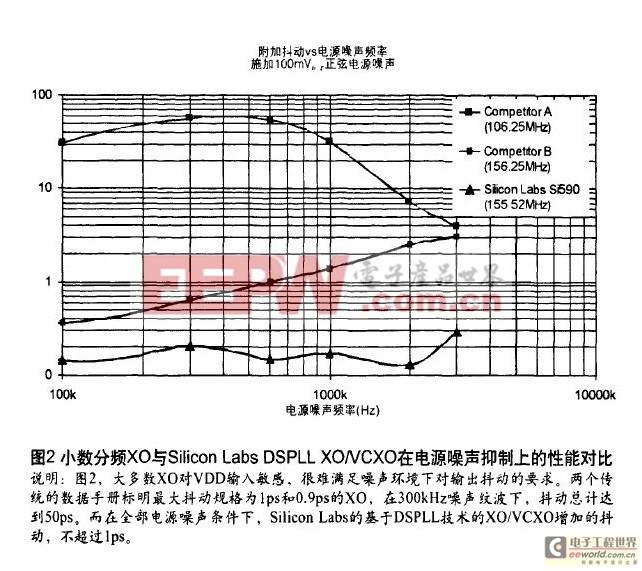

圖2所示為基于小數分頻PLL的xo與基于SilicOrlLabs DSPLL的Xo在電源噪聲抑制上的性能對比。雖然基于小數分頻PLL的振蕩器被證明可達到最大0.9ps RMS的抖動性能,滿足高數據率FPGA SERDES的要求,但是這只適用于理想環境下。在100mV,,的電源噪聲下,競爭對手的解決方案增加了多達40ps RMS抖動,無法滿足高速串行鏈路要求。而SiliconLabs的基于DSPLL技術的XO/VCXo產品依舊滿足要求,在所有測試頻率點上,僅僅影響。增加了0.1ps RMS~0.3ps RMS的抖動。

7 結語

在實際應用中,當前面向FPGA的設計需要對電源開關噪聲有更大抗干擾能力的時鐘。SiliconLabs基于DSPLL技術的時鐘和振蕩器家族是高性能應用FPGA的理想選擇,它們既滿足高速串行鏈路對低抖動性能的要求,又通過集成電源噪聲抑制能力,使實際條件下的操作最優化

評論