基于時間觸發嵌入式系統的設計與應用

1.引言

本文引用地址:http://www.j9360.com/article/227567.htm近年來,嵌入式發展迅速,采用51單片機死循環的事件觸發編程方式已逐漸不能滿足企業對產品穩定性和安全性的要求。目前,嵌入式系統軟件有VxWork、Linux、WinCE、μC/OS-II等,可出于成本和技術上的考慮,微控制器往往不會選取其進行設計。在實際應用中,往往會面臨同時應付多外設、多任務的情況,則對它們的相互調度必不可少。時間觸發嵌入式系統就是這樣的簡單實用的操作系統。

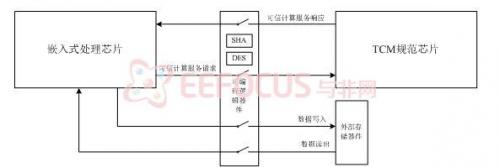

本文設計了基于AVR微控制器的時間觸發多任務調度器并應用于實際。該調度器使用傳遞消息(message)的方式使得微控制器在多個任務及設備間切換。

2.AVR微控制器的結構特點

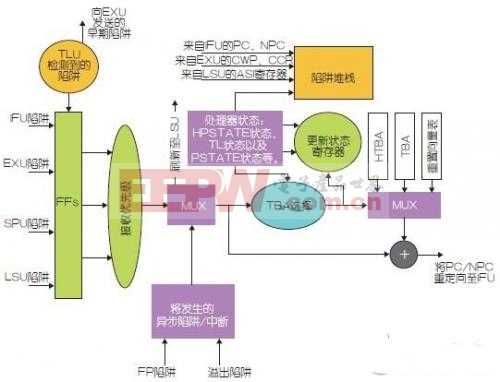

AVR是目前使用以該系列的ATmega128為例說明,它采用哈佛結構,RISC指令集、低功耗、片上資源豐富的特點,極大簡化了外圍電路,使系統更加穩定可靠。其特點為嵌入式系統設計提供了良好的硬件保證。

3.嵌入式兩種觸發方式的對比

在嵌入式系統中,通常采用兩種本質上不同的調度方式:事件觸發和時間觸發。事件觸發方式往往使用多級中斷來實現,其發生時間具有隨機性;而時間觸發方式由一個全局時鐘驅動,系統的行為在功能與時間上都是確定的,即具有可預測性。

3.1 事件觸發方式存在的問題

嵌入式系統開發人員有一種中斷事件絕不會丟失的錯誤觀念,這往往給開發的產品帶來災難性的后果。中斷事件丟失在實際應用中是一個不爭的事實,產生的原因有多方面,但無外乎內因和外因兩種。外因指嵌入式系統外產生的原因,這里主要指中斷源信號丟失或過于頻繁;而內因又可分為硬件原因和軟件原因,硬件原因主要由所用嵌入式器件的中斷嵌套能力所致,軟件原因主要由開發者編程時對任務中斷優先級設置錯誤以及任務處理不當所致。

例如,中斷0是一個高優先級中斷,而中斷1是一個低優先級中斷,則由高優先級中斷激活的中斷服務程序不能被低優先級的中斷打斷。于是,對第二個中斷的響應將被延遲,甚至在一些情況下它有被完全忽略的可能。

如果多個中斷源可能在“隨機的”時間間隔產生中斷,則中斷響應可能被遺漏。實際上,在同時有幾個有效的中斷源的情況下,幾乎不可能創建程序代碼來正確地處理所有可能的中斷組合。并且同時處理多個事件不但增加了系統復雜性,而且降低了系統在所有情況下的行為預測能力。至于使用效率,Metzner討論并得出結論:一個包含27個任務、采用RM調度算法的事件觸發系統,CPU的實際利用率僅為18%.

3.2 時間觸發方式的優勢

在該系統中,設計人員能夠通過仔細安排可控的順序,保證一次只處理一個事件。它的可預測性使其成為安全相關的系統的首選。

Kopetz首先提出:使用基于時間觸發的合作式調度器會使得系統有非常好的可預測性。除可提高可靠性之外,使用該方式有助于減輕CPU的負荷及存儲器的使用量。

4.時間觸發嵌入式系統的設計

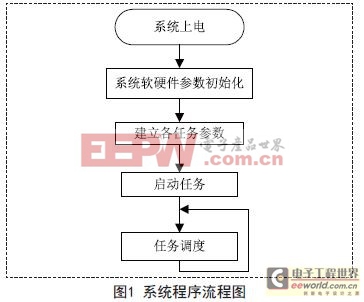

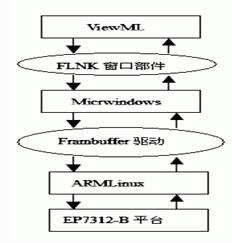

在該調度器中,定時器的設置被分離出來,并使之不依賴于編譯器的數據類型以及處理器的位數,通過修改該部分可以輕松移植到多種硬件平臺。系統整體方框圖如圖1所示:

4.1 消息隊列

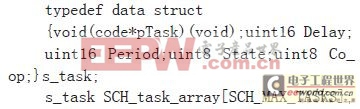

消息隊列是調度器的核心,它是用戶自定義的數據類型,包括了每個任務所需要的信息。盡量將其存儲在DATA區,以供快速存取。

對于基于時間觸發的混合式調度器,使用如下的數據結構,對于每個任務存儲器的開銷僅為8個字節。即使是使用32位處理器,每個任務的開銷也僅為14個字節。

4.2 調度器定時器初始化函數

該函數用來產生驅動調度器的定時時標。

本文所選用AVR系列的ATmega128微控制器具有四個定時器(兩個8位,兩個16位),任一個都能用來驅動調度器,權衡考慮選用定時器0.

void SCH_Init_T0(void){逐個刪除各個任務;停止定時器0;設置時間大小函數;使能定時器0方式;啟動定時器0;}

注:在此期間不可開啟總中斷,即:

電磁爐相關文章:電磁爐原理

評論