高性能PCB的SI/PI/EMC設計是工程中必須解決的問題

目前,越來越多的射頻/高頻設計工程師參與并指導高速互聯設計,且近一半的電路設計人員發現要進行高性能SI/PI設計,就必須采用3D全波模型來處理關鍵互聯問題。

實際上,要在SI/PI/EMI方面實現高性能PCB設計仿真,仿真工具必須具備以下幾點關鍵要求:

第一,必須采用3D全波電磁模型,尤其對關鍵高速走線、過孔、網絡等;第二,能夠仿真模擬PCB上的復雜供電網絡;第三,仿真器(包括場仿真器和路仿真器)必須具備高精度、高速度、大容量的特點;第四,同時提供時域和頻域仿真結果;第五,還必須能與現有的PCB設計流程相兼容。

Ansoft公司的系列電磁場仿真工具再配合專門的SI設計仿真平臺DesignerSI,不僅滿足上述五點要求,而且由于Ansoft場工具均采用獨有的自適應網格剖分技術,因此將電磁場仿真的難度大大降低,長久以來其仿真速度、精度、容量均得到驗證,是工程實用化的工具。場工具幫助互連系統的計者精確地提取并建立互連系統的3D全波模型,隨后在仿真平臺Ansoft DesignerSI中進行系統驗證,提取串擾、眼圖、誤碼率等時域、頻域信息,用于信號完整性/電源完整性及EMC/EMI設計與仿真。千兆比特高速信道設計

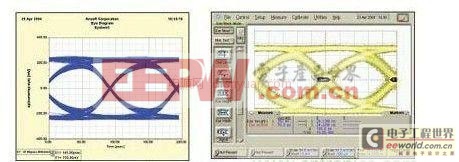

Xilinx公司基于Virtex-II Pro X FPGA的測試評估板,其工作信號速率高達10Gbps以上,Xilinx采用Ansoft系列軟件進行虛擬仿真,完成了對該PCB上收/發高速差分組線 的設計優化,實現高速通信。在設計初始階段,根據實際問題將整個高速串行信道分割為相對獨立的子結構或子系統,如在本例中可分為封裝、PCB走線和SMA 接頭,對各子系統分別進行設計優化,并通過場分析抽取、建立三維全波模型,然后在DesignerSI平臺上通過動態鏈接、協同仿真功能,將各模塊鏈接形成一個完整的信道進行整體性能驗證。這樣做不僅能通過Ansoft參數化設計功能實現各關鍵結構的最優化設計,而且能夠最大限度地提高仿真效率,比如若想 通過對PCB過孔、走線等部分結構的優化調整來提高整體傳輸性能,那么采用這種分解的子系統形式就能幫助設計人員迅速獲得所需數據,避免重復低效勞動。

利用Q2D進行PCB走線的阻抗控制分析,確定差分線的幾何結構和物理參數;利用三維場仿真工具HFSS提取封裝、過孔、SMA連接器、非規則走線等的全波電磁模型;在DesignerSI中鏈接整個信道模型分別在時頻域中進行系統驗證。

在DesignerSI平臺上導入芯片IBIS/Spice模型,通過與Ansoft場工具的動態鏈接完成整個信道的總體驗證,得到眼圖并與實測結果對比。

數模混合電路板的PI和SI問題

一塊六層PCB板,其工作頻帶在1G以下,電源平面上分有2.5v、3.3v和5v三個電源分割,但具有完整的地平面。首先在SIwave中作諧振場分析以便了解電源/地平面在工作頻帶內的整體特性,發現在工作頻帶內(1G以下)會發生多個諧振現象,有14個諧振頻點,同時在SIwave 中可以觀察PCB在各諧振頻點上不同的電壓。由于工作頻帶內的諧振不僅會帶來如電源/地噪聲、SSN等嚴重的電源完整性問題,而且對SI同樣會產 生嚴重影響。本例主要考慮通過在相關位置(如諧振場峰值/谷值位置處)加去耦電容來抑制諧振,從而間接改善SI性能。在SIwave中直接模擬該過程,根據前面得到的諧振分析結果直接仿真去耦電容的影響,為抑制這14個諧振點共加了26個去耦電容,仿真顯示加去耦電容后最低諧振頻點變為1.0133G,在工作帶寬以外。為了了解對SI的影響,選取了一個跨電源分割的信號網絡做S參數掃頻分析,比較加去耦電容前后的S參數變化曲線,發現加去耦電容之后,1G以下信號傳輸特性明顯得到了改善,尤其在700M左右插入損耗和回波損耗有8dB~9dB的改善。

高性能PCB的SI/PI/EMC設計是工程中必須解決的問題" height="257" width="434" style="border: none; vertical-align: mi

高性能PCB的SI/PI/EMC設計是工程中必須解決的問題" height="257" width="434" style="border: none; vertical-align: mi

評論