分享:高速PCB設計EMI規則探討

隨著,信號上升沿時間的減小,信號頻率的提高,電子產品的EMI問題,也來越受到電子工程師的光注。高速PCB設計的成功,對EMI的貢獻越來越受到重視,幾乎60%的EMI問題可以通過高速PCB來控制解決。

本文引用地址:http://www.j9360.com/article/226960.htm規則一:高速信號走線屏蔽規則

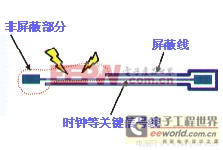

如上圖所示:

在高速的PCB設計中,時鐘等關鍵的高速信號線,走需要進行屏蔽處理,如果沒有屏蔽或只屏蔽了部分,都是會造成EMI的泄漏。

建議屏蔽線,每1000mil,打孔接地。

規則二:高速信號的走線閉環規則

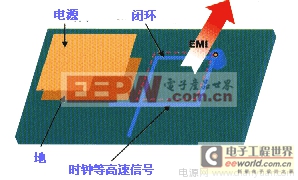

由于PCB板的密度越來越高,很多PCB LAYOUT工程師在走線的過程中,很容易出現這種失誤,如下圖所示:

時鐘信號等高速信號網絡,在多層的PCB走線的時候產生了閉環的結果,這樣的閉環結果將產生環形天線,增加EMI的輻射強度。

規則三:高速信號的走線開環規則

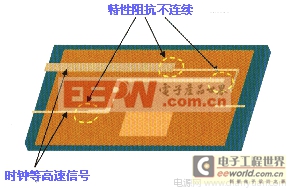

規則二提到高速信號的閉環會造成EMI輻射,同樣的開環同樣會造成EMI輻射,如下圖所示:

時鐘信號等高速信號網絡,在多層的PCB走線的時候產生了開環的結果,這樣的開環結果將產生線形天線,增加EMI的輻射強度。在設計中我們也要避免。

規則四:高速信號的特性阻抗連續規則

高速信號,在層與層之間切換的時候必須保證特性阻抗的連續,否則會增加EMI的輻射,如下圖:

也就是:同層的布線的寬度必須連續,不同層的走線阻抗必須連續。

評論