采用創新降耗技術應對FPGA靜態和動態功耗的挑戰

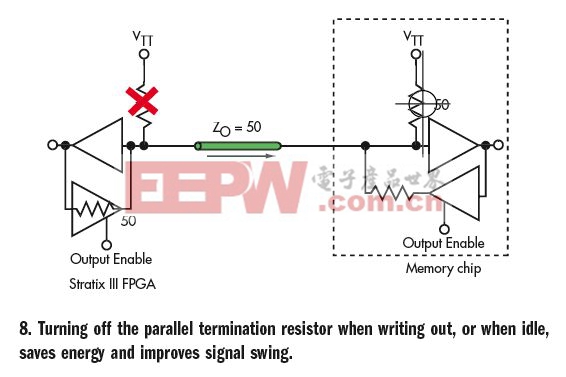

通過支持動態片上終止,根據執行的是讀還是寫操作,FPGA設計師可將并接終止電阻置為“通”或“斷”(開路)狀態。在寫存儲器時,FPGA輸出驅動器阻抗必須匹配傳輸線。但,連至VTT的并接電阻既耗電又減低了信號擺幅。為避免這種情況,可將該電阻關斷(圖8)。

在讀存儲器時,接通并接電阻以終止傳輸線以便減少惡化信號完整性及影響可靠讀取數據能力的反射。

當總線無論執行來自FPGA的寫操作還是空閑時,都將顯著體現動態片上終止的好處。首先,功耗得以極大降低——在一個72位的DDR2總線上,可降低1.6 W的靜態功耗。另外,當寫操作時,可獲得一個純粹的串接線終止。最后,它不再需要大量的板上終止電阻,從而降低了板成本和復雜性。

因DDR3工作在1.5 V(DDR2是1.8 V),所以,DDR3比DDR2省電30%以上。例如,一個帶72腳、具有片上終止的200MHz或400Mbit/s存儲器僅一個接口的功耗就是3.9W。采用動態片上終止(其中,在執行寫或空閑時,并行終止電阻關斷)可降耗1.6 W。若同時采用DDR3和動態片上終止,功耗將降至1.6W,從而一共節省了2.3W。這些數據是僅就一個接口來說的(也即,FPGA中的4個存儲器接口共將省電9.2W)。

向極小的65nm及更精微工藝節點的邁進,能帶來摩爾定律所預期的密度和性能方面的好處。但,性能的提升導致功耗的巨大增加,從而帶來將耗費不可承受功耗的風險。

若不采用降耗措施,靜態功耗將顯著增加。另外,若沒有專門的功耗優化舉措,動態功耗將隨著邏輯容量的增加和開關頻率的升高而增加。

以能力非凡并具創新的架構結合工藝技術和電路技巧方面的進步可應對這些功耗挑戰,它們為當今基于FPGA的日益復雜的設計提供了一個有效和可升級的方案。

評論