采用創新降耗技術應對FPGA靜態和動態功耗的挑戰

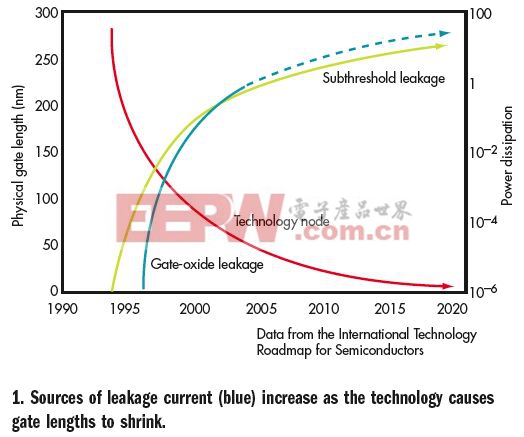

傳統上,數字邏輯并不耗費大量靜態功耗,但隨著工藝節點的不斷精微,這一情況在發生顯著變化。現在,隨著工藝尺度的不斷縮微,數字邏輯中的漏電流成為FPGA的主要挑戰。因在65nm工藝節點靜態功耗會顯著增加,所以,若不采取降耗措施,則功耗將成為一個關鍵問題。因各種原因導致的漏電流的增加,靜態功耗將會顯著增加(圖1)。

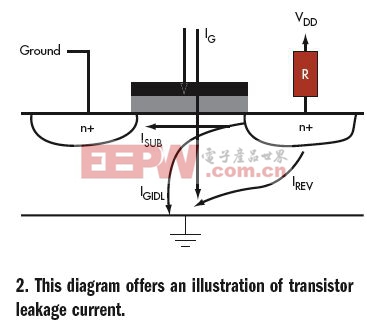

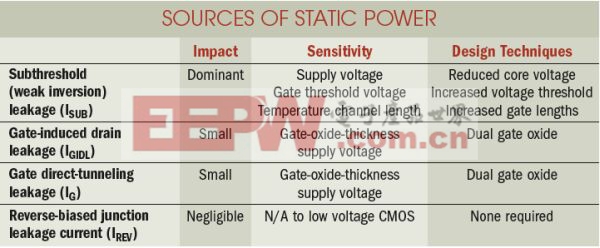

功耗由靜態功耗和動態功耗組成。靜態功耗是FPGA在被編程目標文件(.pof)編程時、但時鐘不工作的狀態下所需的功耗。數字和模擬邏輯都消耗靜態功耗。在模擬系統中,靜態功耗主要包括由其接口模擬電路的靜態電流決定的功耗(圖2和表)。

動態功耗是當器件工作時增加的功耗,它由切換信號及容性負載的充放電引起。影響動態功耗的主要變量是電容充電、工作電壓和時鐘頻率(圖3)。

評論