- 現在主要的代工廠都在生產FinFET晶體管,這些FinFET以創紀錄的速度實現了從設計到現貨產品的轉變。FinFET的發展普及一直都比較穩定,因為與平面器件相

- 關鍵字:

FinFET 動態功耗

- 射頻識別芯片設計中時鐘樹功耗的優化與實現-在RFID芯片中的功耗主要有模擬射頻前端電路,存儲器,數字邏輯三部分,而在數字邏輯電路中時鐘樹上的功耗會占邏輯功耗不小的部分。本文著重從降低數字邏輯時鐘樹功耗方面闡述了一款基于ISO18000-6 TypeC協議的UHF RFID標簽基帶處理器的的優化和實現。##降低功耗主要方法##RTL階段手工加時鐘門控##綜合階段工具插于集成門控單元##時鐘樹綜合階段優化功耗及結論

- 關鍵字:

射頻識別芯片 動態功耗 UHFRFID 芯片設計

- FPGA的應用越來越廣泛,隨著制造工藝水平的不斷提升,越來越高的器件密度以及性能使得功耗因數在FPGA設計中越來越重要。器件中元件模塊的種類和數量對FPGA設計中功耗的動態范圍影響較大,對FPGA的電源功耗進行了分析

- 關鍵字:

FPGA 靜態功耗 動態功耗 觸發率

- 設計CPU需要很多技巧和努力。拿到一個CPU設計并降低其50%的動態功耗需要一系列特殊的技巧,這也是CPU設計人員漫長職業生涯的要取得的技能之一。在成功推出第一款PowerVR Rouge GPU的DOK后,Imagination和Synopsys展

- 關鍵字:

MIPS CPU 動態功耗

- 1.0介紹對于低電壓信號或低功率切換應用,具備MOSFET輸出的光學隔離固態繼電器(SSR,SolidStateRelay)可...

- 關鍵字:

繼電器 動態功耗 設計考量

- 電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

- 關鍵字:

RFID讀寫器模塊 門控時鐘 動態功耗

- 在圖中2.1中,TTL反相順的輸出驅動電路在HI和LO之間交替轉換,Q1或Q2交替處于導通狀態,而不是兩者同時導通。這種電路配置有兩個激勵電路,一個把輸出電壓上拉到HI,而另外一個把輸出電壓下拉到LO,通常稱之為推拉輸

- 關鍵字:

疊加偏置電流 動態功耗 分析

- 邏輯電路每一次跳變,都要消耗超過它正常靜態功耗之外的額外的額外功率。當以一個恒定速率循環時,動態功耗等于功耗=周期頻率*每個周期額外的功率動態功耗最常見的兩個起因是負載電容和疊加的偏置電流。圖2.2說明了驅

- 關鍵字:

驅動容性負載 動態功耗 分析

- 設計者經常僅僅根據所接負載的直流輸入電流要求,冒險使推拉輸出電路的負載達到它的最大直流扇出能力。特別是當設計CMOS總線時這一想法尤其具有誘惑力,因為此時理論上的扇出能力是無限的。實際上重負載的總路線結構

- 關鍵字:

推拉輸出電路 動態功耗

- 在圖中2.1中,TTL反相順的輸出驅動電路在HI和LO之間交替轉換,Q1或Q2交替處于導通狀態,而不是兩者同時導通。這種電路配置有兩個激勵電路,一個把輸出電壓上拉到HI,而另外一個把輸出電壓下拉到LO,通常稱之為推拉輸

- 關鍵字:

疊加偏置電流 動態功耗

- 邏輯電路每一次跳變,都要消耗超過它正常靜態功耗之外的額外的額外功率。當以一個恒定速率循環時,動態功耗等于功耗=周期頻率*每個周期額外的功率動態功耗最常見的兩個起因是負載電容和疊加的偏置電流。圖2.2說明了驅

- 關鍵字:

驅動容性負載 動態功耗

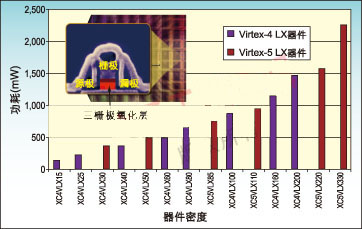

- 過渡至65納米工藝的FPGA具備采用更小尺寸工藝所帶來的優勢:低成本、高性能和更強的邏輯能力。盡管這些優勢能夠為高級系統設計帶來激動人心的機會,但65納米工藝節點本身也帶來了新的挑戰。例如,在為產品選擇FPGA時,功耗的考慮變得越來越重要。很可能下一代設計會需要在功耗預算不變(或更小)的情況下,集成更多的特性和實現更高的性能。

本文將分析功耗降低所帶來的益處,還將介紹Virtex-5器件中所采用的多種技術和結構上的革新,它們能提供功耗最低的解決方案,并且不犧牲性能。

降低功耗的好處

- 關鍵字:

FPGA 低功耗 Virtex-5 靜態功耗 動態功耗

動態功耗介紹

您好,目前還沒有人創建詞條動態功耗!

歡迎您創建該詞條,闡述對動態功耗的理解,并與今后在此搜索動態功耗的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473