基于高速幀同步和相位模糊估計法的FPGA實現

(4)前后方保護

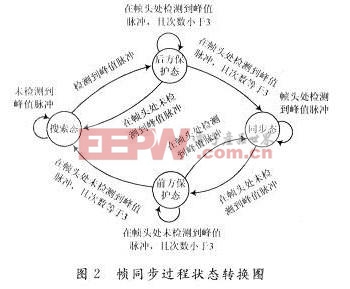

為了減少漏同步和假同步概率,需要進行前后方保護。將幀同步過程分為四種工作狀態,即搜索態、后方保護態、同步態、前方保護態。設定前后方保護系數均為3,即連續檢測到3次峰值脈沖時則判定為同步;連續3次未檢測到峰值脈沖時才判定為失步。前后方保護的工作過程如圖2所示。

(5)恢復相位

對接收符號相位進行適當延遲,以保持與檢測出來的相位模糊值同步,然后用接收符號相位減去相位模糊值,即可將發送符號的相位恢復出來。

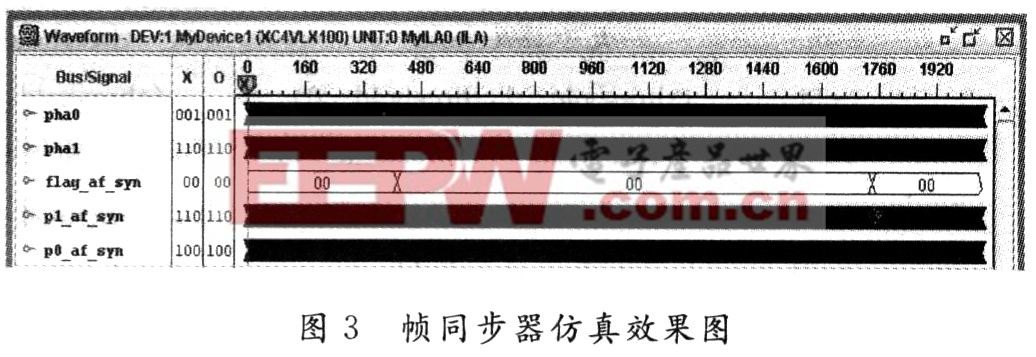

選用Xilinx公司的ISE 9.2作為硬件開發平臺,并采用VHDL編程語言實現本文所描述的高速幀同步器。其中,參數設定如下:同步碼長為58;幀長為2 660;threshold_0為43.500 0;threshold_1為30.763 8。將生成的比特文件下載到Xilinx公司的VIRTEX-4芯片上,通過Chipscope得到的結果如圖3所示。圖中前兩行表示串/并轉換后的兩組相位數據;第3行則為最后給出的同步脈沖信號;第4,5行表示恢復后的相位。

從圖3可以看出,兩個幀同步脈沖信號的距離約為1 330個碼元符號,由于是兩路并行結構,這恰好就是由串行數據一幀長度2 660得到的。

6 結 語

現以符號速率高達320 MSPS的8PSK調制信號為例,研究了能估計相位模糊值的高速幀同步問題。首先提出僅依靠接收符號和本地同步碼來快速確定二維調制符號的幀同步,并同時估計相位模糊值的計算方法。這種方法僅利用符號的相位信息,相對于一般方法減少了一半計算量。給出能夠適應高速數傳系統的并行結構,并且通過FPGA實現驗證了算法的有效性。通過對并行結構以及算法相關參數適當修改,即可對不同速率、不同信噪比的系統有一定的適應性,還可方便地推廣應用于其他MPSK調制信號。

評論