基于高速幀同步和相位模糊估計法的FPGA實現

數字通信中的消息數字流總是用若干碼元組成一個“字”,又用若干“字”組成一“句”。因此,在接收這些數字流時,同樣也必須知道這些“字”、“句”的起止時刻,在接收端產生與“字”、“句”起止時刻相一致的定時脈沖序列,統稱為群同步或幀同步。幀同步的檢出一般可用相關檢測技術完成。以往數據通信中的速率不是很高,相關檢測的問題容易解決,但數字通信的日益高速率化的趨勢,對實時狀態下的相關檢測提出了新的難度挑戰。實際上,很多高速數傳系統比如中繼衛星通信系統,要求用戶星和地面站下行鏈路間的傳輸數據率越來越高,達到了數百兆甚至上千兆的水平。在這樣的高速環境下對數據進行實時的處理,就更加困難。

PSK調制在通信領域得到了廣泛的應用,但存在相位模糊的問題,其一般可通過差分編碼來解決。此法雖然簡單,但需要在發送端加入獨立的差分編碼電路,并在接收端加入差分檢測電路。也有一些方法不用單獨加入差分編碼電路,比如在接收端結合Viterbi譯碼過程來完成相位模糊值的估計,進而進行相位恢復。但這一過程算法復雜,比較耗時。

本文既研究了高速條件下8PSK信號的幀同步問題,同時又對其相位模糊值進行估計。主要依靠并行結構,對傳統幀同步方法進行了簡化和改進,從而同時完成上述兩個任務。并且將該算法付諸FPGA實現,驗證了算法的有效性。

1 傳統幀同步器結構和同步檢測算法

過去已經有很多幀同步技術的研究,其中最普遍的幀同步方法就是周期性地在一幀的起始處集中插入定長的幀同步碼。這種結構通常是用計算接收符號序列與本地同步碼序列相關的方法來檢測幀同步。

對于一維信號,如BPSK調制信號,其相關運算通常可用簡單的同或門來實現。將待檢測比特流與本地同步碼序列對應位進行同或,然后逐位相加。根據和的大小以及符號即可對幀同步以及相位模糊值進行檢測。這種方法雖然簡單,但無法適應如MPSK這樣的二維信號的幀同步檢測以及相位模糊值的估計,因此應用范圍較窄。

2 實現相位模糊估計的幀同步檢測算法

能夠實現相位模糊估計的幀同步檢測算法包含兩部分:

(1)待檢測數據與本地同步碼進行相關運算;

(2)相關值與門限比較,根據比較結構給出相應的峰值脈沖及相位模糊值。

下面以8PSK信號為例對能夠同時實現二維信號幀同步以及相位模糊估計的相關算法和判決方式進行詳細介紹。

2.1 相關算法

由于8PSK信號是二維信號,所以待檢測符號序列可用aiejφi-Ii+jQi,i=0,1,2,…,N-1表示。其中ai為第i個數據的幅度;φi為其相位;N為幀頭碼元長度;Ii,Qi分別表示其實部和虛部。可以用miejθi=i0i+jQ0i,i=0,1,2,…,N-1表示本地同步碼序列,其中:mi為第i個同步碼的幅度;θi為其相位;I0i,Q0i分別表示其實部和虛部。本文選取M序列作為同步碼,并將0,1分別映射為8PSK中相對的0相位和4相位;然后進行8PSK調制。如果幀頭部分碼元發生錯誤(由0變為1,或者相反),其相位就會發生180°偏轉,即由aiejφi變成了aiej(φi+π)。

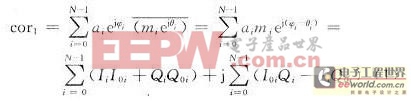

待檢測符號序列與本地同步碼序列的相關值應該為:

得到式(1)的相關值后,一種比較直接的方法就是首先計算相關值的模,然后與門限進行比較來檢測峰值存在與否,若檢測出峰值,再由相關值的實虛部關系(arctan(*))估計相位模糊值。

但是上述方法計算相當復雜,FPGA資源消耗較大,并且不易并發地進行峰值檢測和相位模糊值的估計。所以下面提出一種易于FPGA實現的簡化的算法。

評論