使用RapidIO技術搭建可重構信號處理平臺

2.3 FPGA內部的邏輯設計

在DSP板卡上有一塊Altera公司的Stratix II GX系列的FPGA芯片。這塊FPGA芯片專門用來實現LINK口與RapidIO接口之間的數據轉換,將6路LINK口數據整合到1路RapidIO通路中。數據接收和發送的邏輯結構如圖3所示。

當DSP發送數據時,FPGA的LINK口接收模塊將收到的數據緩存到FIFO中,數據輪詢狀態機按順序檢查FIFO的存儲狀態。當FIFO內的數據滿足RapidIO包最大負載(256 B)時,啟動1次RapidIO數據發送操作。另外,由于LINK口傳輸協議不包含數據長度,所以1次LINK口傳輸的數據長度不可能正好是256 B的整數倍。如果當前FIFO內有低于256 B的數據,而當前LINK口又沒有處于傳輸狀態,也認為LINK口完成了1次數據發送,這時也啟動一次RapidIO數據發送操作。

在每次啟動RapidIO數據發送操作之前,配置寄存器模塊會根據不同的DSP號將對應的路由信息輸入給RapidIO的IP核。RapidIO的IP核負責將輸入的路由信息和數據一起打包并發送出去。

在RapidIO的數據接收端,當RapidIO核接收到數據時,首先檢查數據包包頭中的目標板ID號信息。如果目標板ID號與本地的ID號一致,說明數據包是發往這個板卡的,然后RapidIO核將接收到的數據和DSP地址信息傳遞給數據分發狀態機,由數據分發狀態機根據地址信息將數據分發到對應的FIFO中。最后,由LINK口發送模塊將數據傳給目標DSP。

這種將不同的信號相互交織在不同時間段內,沿著同一個信道傳輸,在接收端再用某種方法將各個時間段內不同的信號提取出來的方式,類似于通信中的時分復用的機制。

2.4 功能仿真

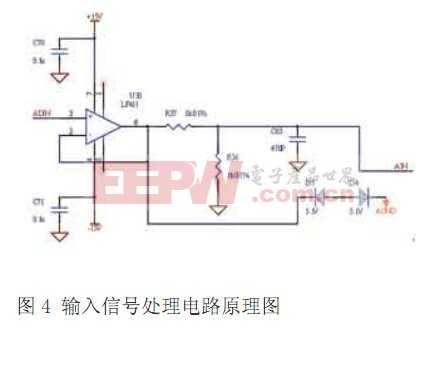

為了驗證rapidIO IP核的邏輯功能和LINK口與rapidIO接口的轉換邏輯功能,將2個rapidIO核的td[3:0],rd[3:0]對接起來。其中一個rapidIO核的后端連接發送數據包的控制邏輯,另一個rapidIO核后端連接接收數據包的控制邏輯。將LINK口邏輯、接口轉換邏輯和rapidIO核邏輯串接起來,然后在數據發送端施加激勵信號,在數據接收端進行數據檢驗。整個過程如圖4所示。

在仿真過程中,最關鍵的部分是驗證rapidIO核的邏輯功能。Altera公司提供的rapidIO IP核的邏輯層接口符合avalon總線的接口時序[4](avalon總線是由Altera公司提出,用于在基于FPGA的片上系統中連接片內處理器和片內外設的總線結構)。對rapidIO核的控制可以參照avalon規范[5]。

2.5 缺陷及解決方案

在系統中,每路LINK口實現300 MB/s的帶寬,如果6路LINK口同時發送數據,總帶寬將達到14 Gb/s,已經超出了RapidIO的IP核所能支持的最大帶寬。這時,RapidIO鏈路將成為數據傳輸的瓶頸,從而造成DSP的傳輸速率降低。另外,當少于3個DSP發送數據時,又會造成RapidIO鏈路的浪費。這像大城市中的交通一樣,在上下班高峰時道路會擁堵,在其他時間,道路又暢通無阻。生活中,很多人會避免上下班高峰時期出行。類似地,在使用此系統時,應該盡量避免在一塊DSP板卡上同時發送6個DSP的數據到其他板卡。

本文提出了一種利用RapidIO技術搭建的可重構的信號處理平臺,并簡要介紹了其邏輯功能的實現。該平臺的最大優勢就是系統的可重構性。使用這樣的信號處理平臺,DSP工程師可以根據不同算法的數據流向重新搭建出更加優化的DSP網絡拓撲結構,從而提高數據的傳輸效率。總之,可重構的信號處理平臺能夠靈活地改變系統中DSP網絡的拓撲結構以適應各種數據流向的應用,為用戶和國家節省大量的設備購買費用和研發時間。

參考文獻

[1] FULLER S.RapidIO:The embedded system interconnect. Wiley,ISBN:978-0-470-09291-0,US.,2005.

[2] RapidIO Trade Association.RapidIO interconnect Specification Rev.2.0.www.rapidio.org,2008.

[3] BOUVIER D,RapidIO:The interconnect architecture for high performance embedded systems.www.rapidio.org,2009.

[4] Altera Corparation.RapidIO megacore function user guide. www.altera.com,2008.

[5] Altera Corparation.Avalon interface specification.www.altera.com,2008.

評論