使用RapidIO技術搭建可重構信號處理平臺

摘 要: 軍事領域常選擇ADI公司的TS201芯片用于信號處理平臺,但由于其采用基于電路交換的LINK口進行連接,難以實現軍方對電子系統設計提出的可重構性的需求。FPGA可以用來實現接口轉換功能,如果利用FPGA將基于電路交換的LINK口轉換成基于包交換的其他形式的接口,就能在不改變硬件連接的基礎上,實現DSP系統的重構。本文介紹了一種基于串行RapidIO技術的可重構的信號處理平臺,并對其中核心的FPGA的邏輯設計進行了討論。

在雷達、聲納、電子對抗等軍用電子設備中,數字信號處理機作為實現信號處理算法的平臺,起著至關重要的作用。在傳統的信號處理平臺中,軍事領域多選用ADI公司的TigerShark系列的DSP芯片作為信號處理單元,在PCB的板內和板間采用高速的LINK口進行互聯。

LINK口是一種源同步接口,可以達到很高的傳輸速度。但是,由于LINK口是基于電路交換的接口,連接的雙方獨占一條通路,LINK口一旦在硬件上連接起來,系統中的DSP網絡拓撲就固定不變了。由于信號處理算法的多樣性,系統中數據流的方向也很不確定,固定的DSP拓撲網絡只能針對一定的算法達到最優,當數據流方向改變較大時,同樣的信號處理平臺的傳輸效率就會大大降低。這時,如果能夠重新調整DSP網絡的拓撲結構,會大大提高平臺的性能。

為了實現系統可重構的特性,需要利用專門的FPGA芯片,將基于電路交換的LINK口轉換成基于(帶有路由信息的)包交換的其他格式的接口進行傳輸。現在比較流行的基于包交換的接口有串行 RapidIO接口、 PCI Express接口和千兆以太網接口等。

串行RapidIO、PCI Express和千兆以太網技術都可以提供高速、可靠的點對點互聯。串行RapidIO技術是專門為嵌入式系統互聯而設計的,只要有足夠多的交換機,就可以實現任意結構的拓撲。PCI Express技術是著眼于最大的兼容PCI總線技術而設計,為了能夠兼容傳統的PCI總線技術,PCI Express的拓撲結構只能是樹形結構。這種結構在PC機和服務器內非常適用,如果合適的話,也能用在嵌入式系統內。但在PCI Express的結構中除了要有交換機,還需要有一個根聯合體來做統一的管理,這增加了硬件的開銷。千兆以太網技術是百兆以太網技術的升級,最初用于局域網內和廣域網內的互聯,是非常可靠的互聯選擇。但千兆以太網技術較前2種技術的效率稍低,而且系統延時較大,不太適合實時嵌入式系統內部的互聯。在這3種技術中,串行RapidIO技術是在嵌入式系統內實現互聯的最佳選擇[1]。

1 RapidIO技術

RapidIO是一種高性能、低引腳數、基于包交換的系統級互聯協議,是專門為多種多樣的嵌入式系統互聯而建立的一種標準[1]。RapidIO接口主要適用于芯片到芯片和電路板到電路板之間的連接。在2008年3月由RapidIO組織公布的2.0版本的規范中,串行RapidIO鏈路可以支持每路1.25、2.5、3.125、5、6.25 GBaud的傳輸速率[2](1,2,2.5,4,5 Gb/s的有效數據率)。現在FPGA的IP核能夠支持的主流配置是x1或x4的鏈路,每路支持2.5 Gb/s或3.125 Gb/s的傳輸速率。因此,如果采用x4的鏈路和3.125 Gb/s傳輸速率,就可以達到雙向各12.5 Gb/s的帶寬。另外,RapidIO也提供了較高級別的錯誤管理和錯誤恢復機制,是一種比較穩定和可靠的互聯選擇[3]。

2 系統結構設計

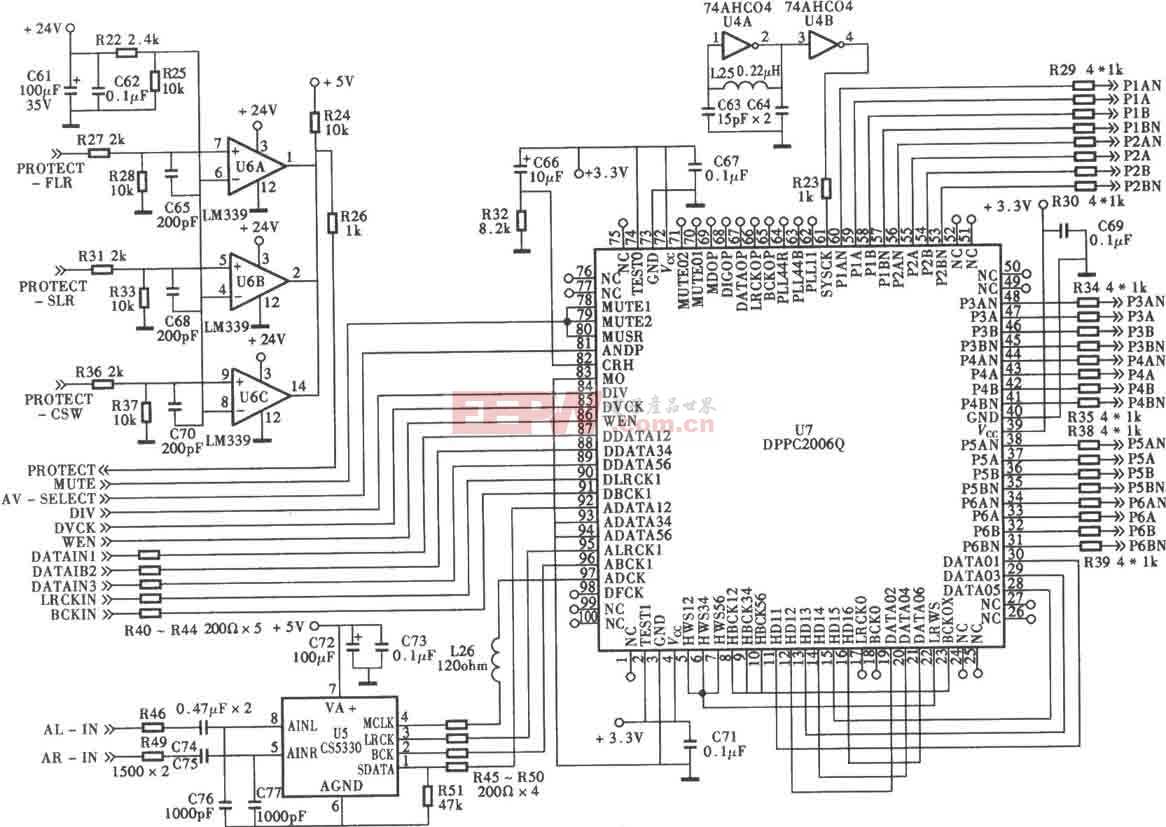

2.1 板卡內DSP的連接結構

DSP板是信號處理系統中最基本的組成模塊,它的結構固定不變。本文選擇ADI公司的TS201系列芯片。每塊TS201芯片帶有4個高速LINK口,其中3個LINK口用于板卡內DSP之間的連接,1個LINK口用來通過FPGA進行協議轉換,轉成串行RapidIO接口,實現與其他板卡之間的連接。板卡上共采用6塊TS201芯片,其拓撲結構如圖1所示。圖中虛線部分表示DSP芯片之間的LINK口連接,實線部分表示DSP與FPGA的LINK口連接。

這種拓撲結構能夠達到板卡內DSP之間較高的傳輸速度,因為每個DSP直接或最多經過一次中轉就能與板上任意其他的DSP進行通信。

2.2 板卡間DSP的連接結構

在DSP板板卡之間用RapidIO接口連接有很多好處。最直接的好處是,由于RapidIO采用的是串行總線,這使得背板上的布線設計不再困難,系統可以擴展得更大。更重要的是,由于RapidIO是以數據包的格式傳送數據的,用戶可以通過改變數據包包頭中的路由信息來改變數據的流向。這使得系統的重構變得十分容易。DSP板在系統中的連接如圖2所示。

在系統內, 任意2片(不同板卡上的)DSP芯片之間都可以建立連接。例如:如果用戶想要將DSP板1上的DSP4中的數據發送給DSP板3上的DSP6,只需在系統上電時提前將DSP板1上的FPGA內部控制路由的寄存器(目標板ID號設為3,目標DSP分配的地址設置為6)通過軟件設置好即可。交換機收到數據后,會根據數據包中用戶配置的路由信息將數據包送往目標DSP板,然后,目標DSP板上的FPGA進一步將數據發送到目標DSP芯片。在下一次的算法設計中,如果數據的流向改變很大時,用戶可以根據數據流向的特點,重新優化DSP網絡的拓撲結構,以適應不同的算法。

重構DSP網絡拓撲的過程在傳統的信號處理平臺中是很難實現的。在多數情況下,由于DSP拓撲結構不夠靈活,算法設計者受限于固定的DSP拓撲結構,只能降低系統的使用效率,從而使大量的DSP資源閑置,降低了系統的處理能力。而在這種新的信號處理平臺架構中,用戶只需要通過軟件界面設置路由信息即可完成整個平臺結構的改變,系統不會因為算法的改變而降低使用效率。

評論