基于PCI總線的微弱信號采集模塊的設計方案

1.引言

本文引用地址:http://www.j9360.com/article/221497.htm隨著微電子技術的廣泛普及、計算機技術的快速發展,現場信息實時采集系統的性能越來越受到大量關注。從測試系統和科研領域產生的動態信息中提取有用數據進行現場實時采集并存儲顯得尤為重要。設計結合實際項目要求,提出基于PCI總線的微弱數據信號采集電路設計方案,將采集數據流通過前端處理電路和AD轉換電路后,在中央控制模塊FPGA控制下將數據流通過PCI總線傳輸給上位機保存,以便分析處理和顯示,從而實現采集系統對微弱數據信號進行高速采集存儲和分析。

2.總體設計方案

在實際研究和現場測試中,數采系統常采用PC機為測試平臺,使用PCI總線作為中介實現數據流采集和傳輸到PC機中進行顯示分析。

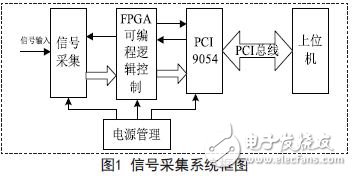

系統常采用傳感器將物理量轉換為電流或電壓信號,經過前端調理電路濾波放大將幅度放大到可測試范圍。但在實際信號采集時存在由系統本身和外界產生的各種噪聲影響,使得傳感器輸出的微弱有用信號被淹沒,因此需要采取有效的措施和算法來抑制噪聲、增大微弱信號幅度,從而提取有用信號,提高系統輸出信號的信噪比,實現微弱信號的高精度采集。基于PCI總線的微弱信號采集系統電路設計可分為:信號采集,FPGA邏輯控制,PCI總線界面以及電源管理等模塊。信號采集即實現模擬信號的接收和將其數字化;FPGA邏輯控制則實現對采集數據流緩沖處理、控制采樣時鐘頻率以及采集模塊與PCI9054界面芯片的握手通信完成數據傳輸。系統設計總體方案如圖1所示。

采集系統上電啟動后,PC機掃描查找采集卡,然后通過上位機對系統進行初始化,并配置采樣參數。系統采集部分在FPGA控制下將接收數據進行調理、AD轉換后存儲到FPGA內部FIFO中緩存,繼而通過PCI總線將數據傳入PC機進行實驗數據的分析顯示和存儲。

3.硬件電路設計

采集系統主要包括AD轉換電路、PCI總線界面電路以及外圍電路。設計采用可編程FPGA和高速AD實現信號采集處理功能,PCI總線界面電路采用控制器PCI9054實現數據傳輸,并通過FPGA控制電路時序。

3.1 數據采集電路設計

系統數據轉換模塊采用1.8V單電源供電的14位高速AD模數轉換器AD9246,最高采樣率為125MSPS,采用多級差分流水線結構。

采樣頻率為70MHz輸入時,無雜散動態范圍為8 5 d B c,信噪比為7 1 。 7 d B c,低功耗設計(395mW@125MSPS)。AD9246為差分輸入器件,輸入信號通過衰減等處理抑制外界干擾,實現在干擾信號比較強時有效的捕捉有用頻帶寬度范圍內的微弱信號。為有效抑制周圍環境噪聲對輸入信號的影響,設計將AD轉換芯片的信號和時鐘輸入設為差分輸入,即采用差分轉換芯片AD8138將模擬信號轉換為差分信號送入AD轉換器,使其在時鐘控制下輸出14位并行數據傳送給后續電路。差分時鐘則通過FPGA分頻轉換產生以實現AD9246內模數轉換周期的控制。

3.2 PCI總線界面模塊設計

PCI界面模塊選用控制器芯片PCI9054來實現PCI總線和本地總線之間信息的傳遞。

PCI9054是PLX公司生產的32位,33MHz的PCI總線通用橋接芯片,具有最高132MB/S的突發傳輸速率,可以將PCI總線復雜的邏輯控制轉換為簡易的本地總線的邏輯控制。設計通過對PCI總線界面電路進行讀寫來實現采集數據的傳輸和上位機控制信號的下傳。PCI9054提供有PCI總線界面、本地總線界面和E2PROM界面。

在設計PCI9054與本地總線界面電路中,將本地總線界面配置為C模式,即設置MODE[1:0]=00,將MODE0和MODE1管腳接地。在系統上電初始化時,PCI9054根據串行E2PROM界面參數配置內部寄存器,采用2Kb的E2PROM芯片93CS56L來存儲PCI9054界面芯片的配置參數。

4.FPGA控制邏輯設計

FPGA控制模塊主要實現對AD采集信號的控制和預處理,以及PCI的界面功能,完成數據的實時采集處理。系統中FPGA選用Xilinx公司的Virtex-4系列芯片XC4VLX25-10SF363I作為設計主控器件,并選擇XCF08PVO48C作為配置芯片。

FPGA內部邏輯包括控制模塊,雙口RAM緩沖模塊,時鐘控制模塊,32位加法器模塊。

其中由控制模塊完成對累計次數,AD讀寫,PCI總線讀寫,采樣時鐘轉換,加法器等的控制功能。其中時鐘轉換即實現數采頻率100MHz和PCI讀數40MHz時鐘的轉換;累加次數控制是通過上位機軟件發送給的,由PCI寫時序控制的,由于AD9246為14位轉換器,系統數據寬度為32位,所以最大可達218次的累加次數。

4.1 FPGA數采邏輯控制

在FPGA對數據采集AD轉換的控制設計中,主要在FPGA中對采樣時鐘分頻以輸出AD時鐘信號和控制允許信號,以及為AD提供不同的采樣頻率和數據接收觸發信號來完成AD數采功能。

模數轉換器相關文章:模數轉換器工作原理

鎖相環相關文章:鎖相環原理

評論