一種新型帶寬自適應全數字鎖相環的設計方案

本方案采用理論分析與硬件電路設計相結合的方法進行了系統設計,并用FPGA予以實現。系統仿真與硬件電路測試結果證實了設計方案的正確性。該鎖相環 的自由振蕩頻率可隨輸入信號頻率的變化而改變,具有電路結構簡單、鎖相范圍廣、鎖定速度快和穩態誤差小等特點。

的自由振蕩頻率可隨輸入信號頻率的變化而改變,具有電路結構簡單、鎖相范圍廣、鎖定速度快和穩態誤差小等特點。

0 引言

鎖相環 是一個輸出信號能夠跟蹤輸入信號相位的閉環自動控制系統,由于其獨特的優良性能,在通信、雷達、測量和自動化控制等領域得到極為廣泛的應用。

是一個輸出信號能夠跟蹤輸入信號相位的閉環自動控制系統,由于其獨特的優良性能,在通信、雷達、測量和自動化控制等領域得到極為廣泛的應用。

全數字鎖相環 (ADPLL)相對于模擬鎖相環

(ADPLL)相對于模擬鎖相環 具有可靠性高、參數穩定、易于集成等特點,因而得到了越來越廣泛的研究,成為各種電子設備中必不可少的組成部件。

具有可靠性高、參數穩定、易于集成等特點,因而得到了越來越廣泛的研究,成為各種電子設備中必不可少的組成部件。

鎖相環 具有三個重要的性能指標:鎖相范圍、鎖相速度和穩定性。為提高鎖相環的各項性能指標,一些學者進行了深入的分析和研究。

具有三個重要的性能指標:鎖相范圍、鎖相速度和穩定性。為提高鎖相環的各項性能指標,一些學者進行了深入的分析和研究。

本文提出了一種基于自適應比例積分的復合控制方式,來克服鎖相環所存在的鎖相范圍、鎖相速度以及穩定性之間相互制約的問題。

1 全數字鎖相環的結構和工作原理

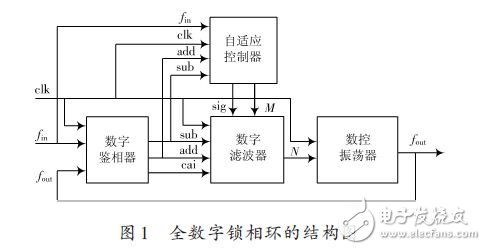

系統由數字鑒相器、自適應控制器、數字濾波器和數控振蕩器四個模塊組成,如圖1所示。下面對各個模塊的工作原理進行詳細的介紹。

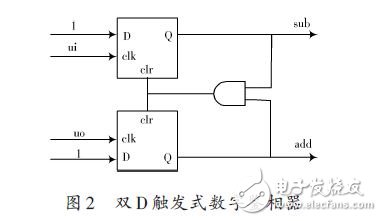

該ADPLL采用雙D觸發式數字鑒相器。鑒相器對輸入信號和輸出信號的相位進行比較,輸出反應相位超前(或滯后)的信號sub(add),sub 和add 不僅反映了相位的超前滯后情況,其脈沖寬度也反映了相位誤差的大小。其結構框圖如圖2所示。

自適應控制器模塊主要起到調節環路帶寬的作用。控制器一方面對輸入信號進行鑒頻,另一方面對鑒相誤差信號sub、add進行量化,根據量化值計算出濾波器控制參數M,如果輸入信號頻率發生較大的變化,控制器發出控制信號sig,將控制參數M 賦給濾波器,對周期性復位可逆計數器和不復位可逆計數器進行初始置位,以此來迅速地實現頻率捕捉和環路帶寬的調整。

環路濾波器主要由周期性復位可逆計數器和不復位可逆計數器構成,其中系統高頻時鐘clk為其同步時鐘信號,add和sub作為兩個計數器的加、減計數使能控制信號。計數使能信號為高電平時,兩計數器在clk時鐘上升沿到來時進行相應的加1或減1操作,計數使能為低電平時則保持計數值不變。當輸入信號fin 上升沿到來時,將兩計數器的計數值進行移位相加,相加結果送入鎖存器,作為數控振蕩器的控制參數N,然后將比例計數器復位。

數控振蕩器模塊采用除N 計數器式數控振蕩器,在系統高頻時鐘clk的控制下工作,分頻參數N 來自環路濾波器的輸出值,如果計數器計數值小于N,每一次clk 上升沿到來時,計數器加1,計數到N 時,計數器復位,輸出fout 取反。

2 系統的建模與分析

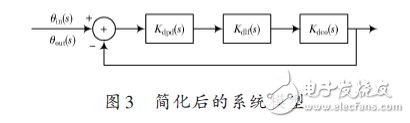

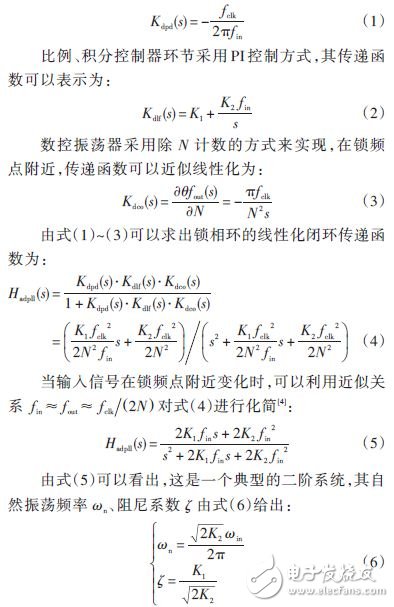

由以上分析可知,當輸入信號在鎖頻點附近變動時,鎖相環的數學模型可以用圖3來表示。

圖3 中,θin (s) 為輸入信號fin 的相位,θout (s) 為數字壓控振蕩器輸出信號fout 的相位;Kdpd (s)、Kdlf (s)、Kdco (s) 分別為數字鑒相器環節、數字濾波器環節、數字壓控振蕩器環節的傳遞函數。

2.1 系統數學模型

設系統高頻時鐘信號為fclk,由雙D 觸發器型鑒相器的工作原理可以求出鑒相模塊的傳遞函數為:

濾波器相關文章:濾波器原理

濾波器相關文章:濾波器原理

塵埃粒子計數器相關文章:塵埃粒子計數器原理 鑒相器相關文章:鑒相器原理 數字濾波器相關文章:數字濾波器原理 鎖相環相關文章:鎖相環原理 鎖相放大器相關文章:鎖相放大器原理

評論