基于ARM和FPGA的線陣CCD測徑系統的設計

近幾年來,電線、電纜、光纖等產品的需求量大大增加,外徑尺寸的質量控制成為許多生產廠家急需解決的問題。傳統的測試手段有以下幾種:(1)手工測量法:采取先加工后測量的方法,精度一般,人為因素多,勞動強度大,信息反饋慢,直接影響了線材的質量和生產效益。(2)接觸法測量:精度較高,但易磨損,重復測量精度差。(3)光電二極管陣列測量法:速度快,易處理,但精度差。因此,必須有一套高精度的實時在線檢測系統,一方面可使生產人員及時了解線徑的大小及偏差,另一方面給生產機構伺服系統提供正比于偏差的反饋量,實現反饋控制。以線陣CCD高精度傳感器為核心組成的動態外徑測量儀器具有速度快、精度高、抗干擾能力強等優點[1],成為最為理想的工業在線檢測手段之一。

1 CCD測徑原理

電荷耦合器件CCD(Charge-coupled Devices)是20世紀70年代初發展起來的新型半導體集成光電器件。目前,CCD技術已發展成一項具有廣泛應用前景的新技術,成為現代光電子學與測試技術中最受關注的研究熱點之一。

線陣CCD測量直徑系統的原理圖如圖1所示。圖中,1為光源;2為透鏡,作用是匯聚光能;3是一片毛玻璃,其作用是盡可能使光能夠均勻分布;4為被測線纜;5就是要在其上成像的線陣CCD傳感器。線纜直徑測量的原理如下:經光源1發出的光通過一系列透鏡2后校正為近似的平行光。當光由毛玻璃片3透過線纜后通過成像物鏡在線陣CCD的光敏面上成像,最后經CCD的輸出電路將電荷轉化成電壓量輸出。

CCD輸出的是視頻脈沖信號,其中每一個離散信號對應著CCD上的一個光敏單元的輸出。同時CCD視頻信號需要經過處理電路轉化為標準信號,以便進一步對其處理。當測量線纜直徑時,由于線纜的遮擋部分沒有光透過,所以線纜的直徑與光敏單元總長度減去透過縫隙光敏單元長度成正比關系,根據成像物鏡放大(縮小)的倍數可以測得線纜的直徑尺寸。

被測線纜直徑的尺寸計算公式為:

D=(L-hn)/β (1)

式中L是CCD有效測量光敏單元總長度,h是光敏單元的脈沖間距,n為透過縫隙的光敏單元個數, β則為成像物鏡的放大倍數。

因此,只要測出n,就可以計算出被測線纜的直徑。

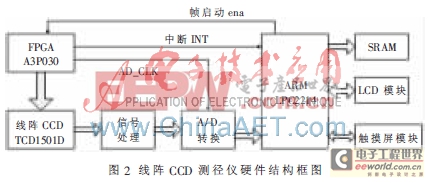

2系統硬件設計

測量線纜直徑的硬件結構框圖如圖2所示。選用NXP公司生產的嵌入式微處理器LPC2214作為控制器,可以滿足線纜生產行業對線纜直徑實時性、高速性和精確性的測量和控制,同時具有高性能、低功耗、價格低廉的特點,片內資源豐富,具有極高的集成度,支持工業級應用。

由于CCD光電傳感器的轉換效率、信噪比等光電特性只有在合適的時序驅動下才能達到設計所規定的最佳值,輸出穩定可靠的信號,因此系統中采用FPGA芯片(選用Actel 公司的A3P030)進行CCD驅動電路的設計。

2.1 主控制模塊的設計

ARM嵌入式處理器是整個硬件系統的核心,LPC2214集成了豐富的片上功能模塊,主要有:外部存儲器控制模塊(EMC)、系統控制模塊、通用并行I/O口、串行通信口(UART)、I2C接口、SPI接口、CAN總線控制器、定時器控制模塊、脈沖寬度調制器、A/D轉換器、實時時鐘控制器等。LPC2214集成了Flash存儲器和靜態RAM,其中Flash存儲器可用作代碼和數據的存儲。

系統中被測線纜被均勻照明后,經光學成像系統按一定倍率成像于線陣CCD傳感器上,線陣CCD在驅動脈沖的作用下,將采集到的光信號轉換成電信號輸出,將處理后的模擬視頻信號送入A/D轉換器。LPC2214所起的作用是:當全部像敏單元信號轉化結束之后,A/D器件停止工作,此時給ARM微處理器LPC2214一個中斷信號,通知LPC2214將SRAM中的所有數據通過數據總線讀取到數據存儲器內。處理器LPC2214對于所有數據根據數據處理程序進行處理,并將處理結果通過數據總線輸出到LCD顯示器上,便于進行實時監測以及后續控制。

2.2 CCD驅動電路的設計

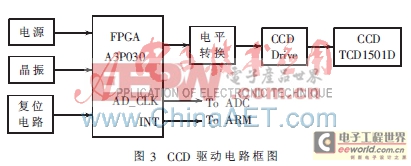

CCD驅動電路的設計是線纜直徑測量系統中的一個關鍵問題,由于不同廠家、不同型號的CCD器件的驅動電路各不相同,而成品CCD的驅動電路價格昂貴,不便使用推廣[2]。本設計中采用了Actel 公司的FPGA器件A3P030配合CCD專用驅動器組成了CCD的驅動電路。經實驗證明,本電路能夠可靠地驅動CCD。

2.2.1 TCD1501D的時序要求

根據項目的技術要求,本系統選用日本TOSHIBA公司的TCD1501D型線陣CCD作為傳感器。該器件具有優良的光電特性,有5 000個像元。根據CCD的驅動信號的時序[3],TCD1501D需要六路驅動信號,它們分別是:兩個時鐘脈沖Φ1和Φ2,轉移脈沖SH,復位脈沖RS,鉗位脈沖CP,以及采樣脈沖SP。TCD1501D采用兩相驅動脈沖方式工作,設計中所選擇的驅動頻率是其典型值:fΦ1=fΦ2=0.5 MHz,相應的數據輸出頻率是fRS=1 MHz。該CCD器件一行輸出的信號是5 076像元,包括13個虛設單元信號、48個暗信號脈沖,然后是S1 到S5000的有效像素單元信號、9個暗信號脈沖和2個奇偶檢測信號及1個啞元信號,之后可以有任意個空驅動,所以有TSH≥5 076TRS,從而可以計算出每次光積分所需的最短時間為:TSH≥5 076TRS=5 076 ?滋s=5.076 ms。根據相關技術資料[3],TCD1501D的六路驅動脈沖之間需要滿足特定的時序關系:Φ1、Φ2必須反相,占空比1:1;SH的高電平至少要保持500 ns,它的脈沖寬度要小于Φ1,延時至少100 ns;RS與CP時鐘的占空比為1:4。

2.2.2 TCD1501D的驅動電路設計

驅動電路結構如圖3所示。本設計中FPGA可編程邏輯器件A3P030負責產生線陣CCD器件TCD1501D六路驅動信號,該芯片有3萬個系統門,以Flash架構為基礎,是一款低功耗、掉電非易失的FPGA,配上電源、晶振和復位電路就可以構成最小系統。A3P030的I/O口電壓為3.3 V,其輸出低電平最大值VOL=0.4 V,輸出高電平最小值VOH=2.4 V,而線陣CCD傳感器TCD1501D要求的信號輸入高電平的最小值VIL=4.5 V,因此兩器件之間電平不匹配,不能夠直接驅動CCD工作,這里使用電平轉換器SN74ALVC4245進行電平轉換,再經CCD專用的驅動芯片調整,最后得到可靠的驅動信號。這個電路結構簡單,抗干擾性好,同時,還具有低功耗、高精度、時序配合準確的優點。

評論