多路讀寫的SDRAM接口設計

(3)刷新操作

動態存儲器(Dynamic RAM)都存在刷新問題。這里主要采用自動刷新方式,每隔一段時間向SDRAM發一條刷新命令。刷新過程如圖4所示。

3 接口電路的設計

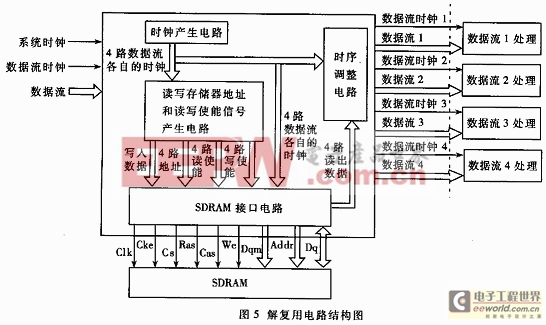

(1)解復用電路

本解復用電路主要完成將1路高速數據流解復用為4路數據流,其結構框圖如圖5所示。1路數據流進入解復用器后,經過SDRAM緩沖,解復用為4路數據流。

由于要解復用為4路數據流,為了充分利用時隙,滿足高速的要求,采用4個bank的SDRAM,各路數據緩沖對應不同的bank。為簡化設計,數據流1的緩沖區定為bank0,數據流2的緩沖區定為bank1,數據流3的緩沖區定為bank2數據流4的緩沖區定為bank3。對于每路數據實際上是以高速率集中寫入,然后以低速率均勻讀出。

(2)SDRAM接口電路的時序控制

高速數據流的速率為3M字節/秒,采用的系統時鐘為20倍的字節時鐘。送入SDRAM的時鐘為60MHz系統時鐘。在一個字節時鐘內對SDRAM的操作最多有5次(1次讀,4次寫),而且為了滿足刷新的要求,每個字節時鐘進行一次刷新操作。根據SDRAM的時序要求,這樣的操作是難以實現的。因而要通過多bank操作,盡量做到時分復用來實現。圖6給出了在一個字節時鐘周期的內數據流1進行讀寫操作,其它3路數據進行讀操作的命令排序時序圖。可以看出通過多bank操作,時分復用,在20個系統時鐘節拍內所需的讀寫操作命令剛好很緊湊地排開。

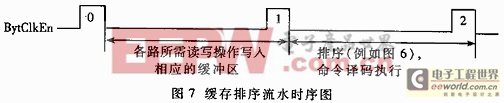

(3)SDRAM接口電路

SDRAM接口電路中需要專門操作緩沖區存儲一個字節時鐘周期內的操作,以備下一字節時鐘的排序。為了方便處理,對每路數據的緩沖操作內容(或讀或寫)放在一個緩沖區。由于數據流的連續性,排序的同時仍然會有操作要求,因此每路的操作內容緩沖區分為兩塊。對一塊緩沖區寫入時,讀出另一塊緩沖區中的操作內容,進行排序、譯碼、執行。根據字節時鐘切換對緩沖區的讀寫,從而避免沖突。對于從SDRAM讀出的數據,每路數據寫入相應的讀出數據緩沖區。同樣每路的讀出數據緩沖區也分為兩塊,根據字節時鐘切換讀寫。

由于一個字節時鐘周期內,每路所需的操作最多有2次,每路的操作內容緩沖區只需兩個單元(每個單元存儲了此次的讀寫使能信號、寫入數據、地址)即可。對于讀出數據緩沖區,由于一個字節時鐘每路數據最多執行一次讀操作,所以讀出數據緩沖區只需要一個字節。這兩類緩沖區容量都小,因此人部用寄存器來實現,控制簡單。

整個接口電路的結構框圖如圖8所示。

4 SDRAM接口的實現結果

針對MT48LC8M8A2的SDRAM,采用同步設計方法,用Verilog HDL硬件描述語言建立模型,接口電路已經調試通過,規模為2100門(NAND)。整個解復用電路也已經調試通過。

評論